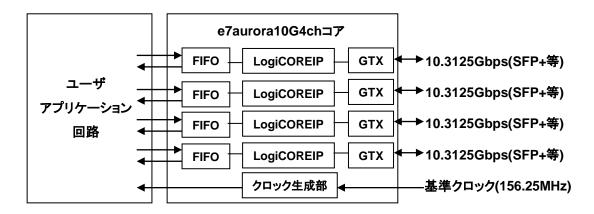

## e7 Aurora10G 4chコア

多FPGAボード間の高速データ伝送を、簡単にサポートします。 ボード間のクロックの周波数同期も実現します。

## <mark>Xilinx LogiCORE IP Aurora 64B/66Bをベー</mark>スに、4ch化を実現

Coregenにより生成できるLogiCOREをベースに、HDL部分を改良し、下記の機能を実現しました。

1. 4ch独立でのリンクを確保。

E-mail:sales@e-trees.jp

このカタログは2013年4月現在のものです。内容は予告なく変更することがあります。

- →別々のFPGA同士でリンクを確立できます。

- 2. GTXでの受信CDRクロックをベースに、ユーザクロックを生成可能。

- →1つのFPGAのクロック周波数を、他FPGAで共有できます。

- 3. FIFOにより、ユーザアプリケーションが必要とするデータ幅やクロック周波数に対応可能。

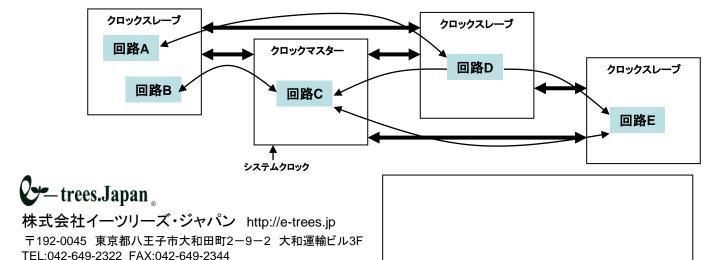

## <mark>ボード間、ユニット間接続を跨いだ大規模FPGA分散環境が構築可能</mark>

マスターFPGAのユーザクロック周波数を、スレーブFPGAで共有できます。 これにより、信号処理やストリームデータ等の連続的なデータも、複数FPGAで分散処理が可能です。