FPGA SATA開発キットは,SATAとFGPAを搭載したコンパクトなボードAxfmc6040とHDLで実装されたe7SATA IPコアで構成される,FPGAからSATAデバイスにアクセスする製品開発および研究のためのキットです.

FMC LPCコネクタを介して,他のFPGAボードなどとの通信も可能です.

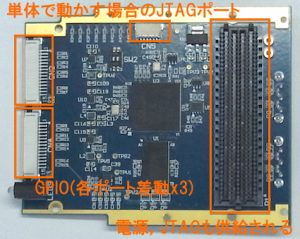

主要部品のスペック

- FPGA XC6SLX45T-3C

- DDR3SDRAM MT41K128M16JT-125 (2Gb)

- IO

- CSI-2 x2

- FMC LPC

- SATAポートx2

- その他

- LEDx8 + LEDx1

- プッシュボタンx1

ページ下部の写真もあわせて,ご参照ください.

クイックスタートガイド(動作確認)

1. Zedboardを使って動作確認

ZebdoardのFMCにAxfmc6040を接続して動作確認をすることができます.Zedboard側には,下記Zedboad用のファームウェアを合成しておく必要があります.

0. 準備

- e7SATAボードのROMにファームウェア(MCS)を書き込む

- Zedboardをe7SATAアクセス用のモジュールを組み込んだファームウェアで起動,その上でXillinuxを起動させる

- Xillinux上でテスト用のソフトウェア一式を展開

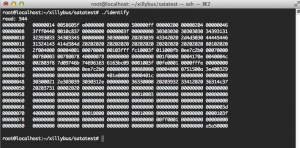

1. Identifyコマンドの実行

- ./lvds_reset でLVDSの経路を初期化

- ./identify を実行

- SATAディスクからIdentify情報が返されることが確認できます.

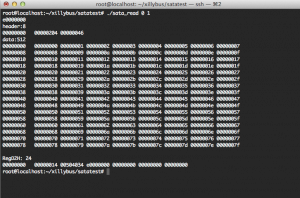

2. SATAからデータを読み出す

- ./lvds_reset でLVDSの経路を初期化

- ./sata_read を実行

- SATAディスクの0セクタ目から8KBのデータの読み出しが確認できます

3. SATAのデータ読み出しスループットを計測する

- ./lvds_reset でLVDSの経路を初期化

- ./sata_recv を実行

- このプログラムを実行すると(引数で指定した値 + 1)*16セクタ= (引数で指定した値 +1) * 8KBのデータを連続して受信するまで待機します

- はじめの16セクタを受信した直後から,最後のデータを読み出すまでの時間を計測します.

- 別のターミナルで,./sata_read_cmdを実行

- 引数は,開始セクタ番号 セクタ数です

- sata_recvを使って速度を測定する場合は,sata_recvの引数に指定した値nに対して,16*(n+1)の値を指定してください

- ./sata_recvが指定したセクタを受信した後,スループットが表示されます.

4. 任意のFISパケットを投げる

identfiy.cを参考に5DWORD(20Byte)のデータにFISコマンドを設定することで,任意のFISコマンドを発行できます.

リソース(サポートページからダウンロードしてください)

- 回路図

- e7SATAプロジェクト一式(Xilinx ISE 14.7用)

- 20140904版ROM書き込み用MCS

- e7LVDS IPコア ドキュメント

- 動作テスト用Zynqプロジェクト一式(別途Xillybusが必要)

- 動作テスト用ソフトウェア(別途Xillinuxが必要)

ファームウエアのご利用には,以下の使用許諾契約への同意がひつようです.

e7SATA IPコア使用許諾契約書,e7lvds IPコア使用許諾契約書

IPコア内部構造とインターフェースについて

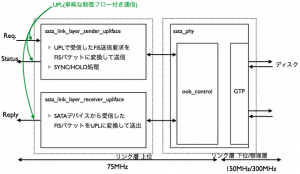

ReqのUPLにはディスクに送信したいFISパケットをそのまま入力します.

StatusのUPLには,ReqへのFIS送信結果が返されます.32bitの固定長データで,正常終了=0x00000001,再送タイムアウト=0x00000002です.

ReplyのUPLからは,ディスクから送られてくるFISパケットが出力されます.ただし,ディスクから返されるFISパケットの先頭にバイト数を示す32bitのヘッダが付与されます.

IPコア内部構造とインターフェースについて

ReqのUPLにはディスクに送信したいFISパケットをそのまま入力します.

StatusのUPLには,ReqへのFIS送信結果が返されます.32bitの固定長データで,正常終了=0x00000001,再送タイムアウト=0x00000002です.

ReplyのUPLからは,ディスクから送られてくるFISパケットが出力されます.ただし,ディスクから返されるFISパケットの先頭にバイト数を示す32bitのヘッダが付与されます.

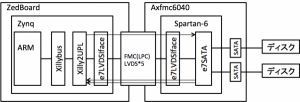

クイックスタート用の回路とLVDSインターフェースについて

FMCで他ボードのFPGAと通信するために,e7LVDSIfaceを使っています.e7LVDSIfaceはe7SATAコアへのUPLポートとの単純なブリッジを提供しています.下図はクイックスタートとして提供しているサンプルシステムのオーバービューです.

ボード外形・概要

Zynq用Xillybusファームウェアの合成

次の手順で合成してください

- XillybusよりZedboard用のデモプロジェクトをダウンロード

- Xillybusの手順にそってデモファームウェアを合成

- 本ページよりXillybus用のe7SATAテストリソース一式をダウンロード

- ダウンロードしたe7SATAリソースをXillybusデモプロジェクトの下に展開

- 展開したディレクトリ下のsourceに移動し,setup.shを実行

- 展開した中のISEプロジェクトファイルで合成

e7SATAテストリソースからみて../systemや../oncerunにXillybusのリソースがみえている必要があります.

よく使うFISパケットの例

よく使うFISコマンドを紹介します.

IDENTIF

デバイス識別情報を取得します.リクエストパケットのフォーマットは次の通りです.

| 0x00ec8027 |

| 0xe0000000 |

| 0x00000000 |

| 0x00000000 |

| 0x00000000 |

デバイスからは,次のようなパケットがかえってきます.

DMA READ EXT

ディスクから指定したセクタのデータを読みだすためのコマンドです.

| 0x00258027 |

| 0xe0000000 + (lba[23:0] & 0x00FFFFFF) |

| lba[47:24] |

| sector & 0x0000FFFF |

| 0x00000000 |

ここで,lbaは読み出しを開始するセクタアドレス,sectorは読み出すセクタ数です.

デバイスからは,次のように,パケット長(4Byte)とデータを示すフィールド(4Byte)のヘッダに続いてデータが出力され,最後にRegD2Hパケットが送られてきます.

FISパケットの制約から8KB以上のデータは複数のパケットに分割されます.その場合,

HEADER DATA HEADER DATA … HEADER DATA RegD2H

となります.

DMA WRITE EXT

ディスクにデータを書き出すためのコマンドです.

| 0x00358027 |

| 0xe0000000 + (lba[23:0] & 0x00FFFFFF) |

| lba[47:24] |

| sector & 0x0000FFFF |

| 0x00000000 |

ここで,lbaは読み出しを開始するセクタアドレス,sectorは読み出すセクタ数です.

このコマンドを送った後に,データを示す4Byteのヘッダ 0x00000046に引き続いてデータを送るとディスクに書き込まれます.

データが受理されるとRegD2Hが返送されます.

リードデータ同様,FISパケットの制約から8KBを超えるデータは8KBずつに分割して転送する必要があります.各FISパケットが受理される毎にRegD2Hパケットがディスクから送り返されてきます.