VHDLで設計するハードウェアモジュールに限らず、一般に複数のものを組み合わせて利用することは困難なことです。そのため、様々なプラットフォーム上で様々な方法が考えられています。

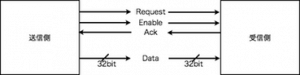

e-trees.Japan,Incでは、ハードウェアを構成するモジュール群の物理的な接続を

- Reqeust,Ack,Enableの3つの制御信号

- Strobe信号(オプション)

- データバス

に限定し、その上でモジュール同士のデータ授受をシリアライズ化したパケットとしてやり取りすることで、簡単なモジュール間接続を実現しています。この仕組みをUPLと名付けています。この仕組みにより複雑なデータパスの信号遅延の考慮やモジュールのつなぎ替えによるコード改変の手間を大きく削減することができます。

UPLでのデータ転送と転送フロー

UPLでモジュール間を接続するためのポートは,次の通りです。

データバス幅は原理的にはモジュール間で自由に取り決めることができますが、多くの場合,8bit/16bit/32bit/64bit/128bit/256bitなどを利用しています。

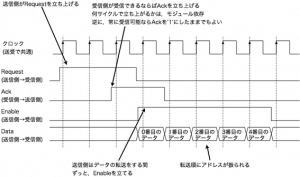

UPLでのデータ転送のフローは次の通りです。

送信する側は,

- データ送信に先立ってAckが立ち上がるまでRequestをたてる(すでにAckが立っている場合には,省略可能)

- Ackが立ち上がったらEnableをたてると同時にデータ転送を開始

- データ転送が終わると同時にEnableを下げる

受信する側は,

- 受信できる準備が整っていればAckを立ち上げる

- Enableの立ち上がりからクロックの立ち上がりでデータを受信

- Enableが立ち下がったら受信を終了

ほかのストリームベースのプロトコルと違って,データ転送を開始したらデータ転送の完了まで停止できない分,シンプルな構成になっています.

オプションのStrobeをつけることで,Enableを’1’にしている期間のうち有効なデータを指定することができます.(Enableが’1’でStrobeが’1’のデータのみを有効データとして扱う)

特許

特開2002-208982(P2002-208982A)