ネットワークアプリケーション開発・実験にぴったりのスティック型FPGAボードです。

専用のUDP/IP IPコアが付属していますので、WebPackISEの開発環境があればすぐに開発が始められます。

- Pmodに対応。各社から発売される様々なモジュールを利用できます。

- ブレッドボード配置に対応。ブレッドボードにそのまま挿すことができます。

- ISE WebPackを使って、無料で開発が可能です。

- マザーボードを用意すれば、複数台並べて配置し、2ポート以上の構成も可能です。

- イーサーネットは、10/100Mbpsに対応。(GbEは対応していません)

exStickスペック

| FPGA | XC6SLX16-2CSG225C |

| Ethernet PHY | DP83848VV (10/100Mbps) |

| Configuration ROM | 25P40VP (4Mbit) |

| User-application ROM | 25PE10VP (1Mbit) |

| 汎用ユーザI/O(2.54mmピッチ)数 | 42本 |

| DIPスイッチ | 4入力 |

| プッシュボタン | 1個 |

| ユーザI/O数 | 42本 |

| オンボード・クロック (PHY供給クロックと共用) |

25MHz |

| その他 | e7UDP/IP IPコア (本製品でのみ使用可能なライセンス) |

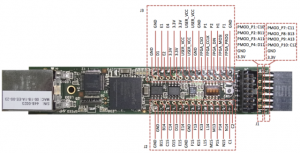

exStick外部IOコネクタの接続先詳細

| コネクタ名 | 接続先 | ピン数 |

|---|---|---|

| J1(10pin) | GND | 2 |

| Vcc(3.3V) | 2 | |

| FPGA BANK0 シングルエンドIO | 8 | |

| J2(26pin) | GND | 4 |

| FPGA BANK1 差動IO | 20(10ペア) | |

| FPGA BANK3 | 2 | |

| J3(26pin) | GND | 6 |

| Vcc(3.3V) | 4 | |

| VccIO | 4 | |

| FPGA BANK3 差動IO | 6(3ペア) | |

| FPGA BANK3 シングルエンドIO | 3 | |

| FPGA BANK3 差動IO/GCLK | 2(1ペア) | |

| FPGA BANK3 シングルエンドIO/GCLK | 1 |

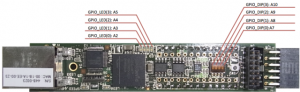

exStickオーバービュー

このピン配置は参考画像です。正しくは回路図に準拠して設計してください。