前回は exStickGE 上に載せた MicroBlaze で Linux を動かしてみました.

ただしこの状態ではネットワークに接続できません.

本ボードの特徴である Ethernet を有効活用すべく追加しました.

追加作業

前回に引き続き Linux 上での作業です.

事前に使用する予定のソースコード(mii2rgmii.v)をダウンロードしておきます.

ハードウェア上の作業

Vivado を起動します.

source /tools/Xilinx/Vivado/2020.1/settings64.sh vivado &

前回のプロジェクト linuxprj を開きます.

その後左の Flow Navigator->PROJECT MANAGER->Add Sources をクリック.

Add or create design sources で次へ進み Add Files で

最初にダウンロードしておいた mii2rgmii.v を追加します.

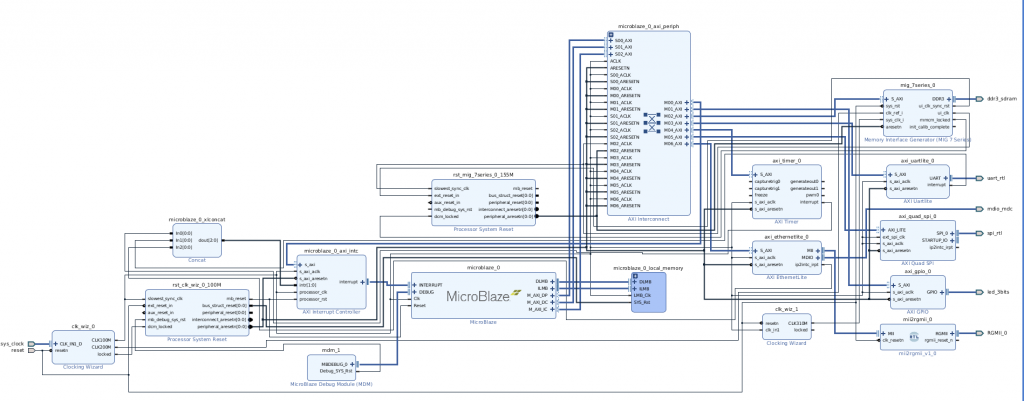

次は 左の Flow Navigator から Open Block Design でブロックデザインを開きます.

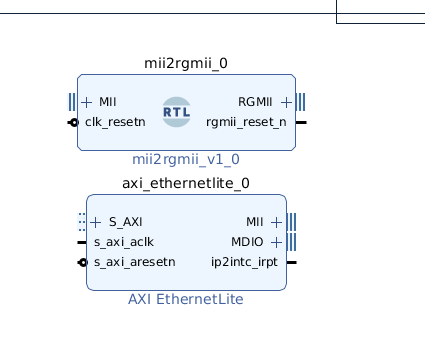

右クリックし Add IP… から AXI EthernetLite を追加します.

また右クリックし Add Module… から mii2rgmii モジュールを選択し追加します.

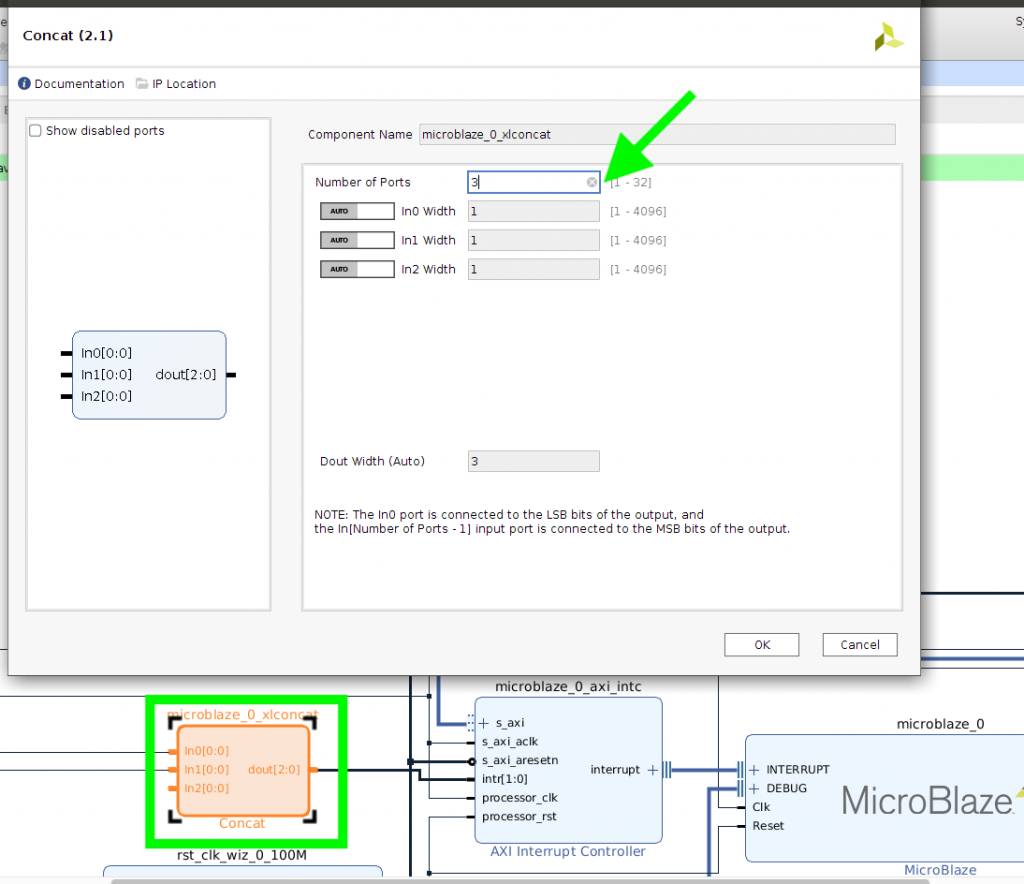

次にAXI Interrupt Controller につながる Concat をダブルクリックします.

Number of Ports を 2 から 3 へ変更します.

配線は以下の通りです.

- AXI EthernetLite の MII と mii2rgmii の MII を接続.

- AXI EthernetLite の ip2intc_irpt と Concat の In2 を接続.

- 外部入力端子の reset と mii2rgmii の clk_resetn を接続.

- mii2rgmii の RGMII を右クリックし Make External で外部に入出力を生成.

- 上部の Run Connection Automation で MDIO と S_AXI を自動接続.

ブロックデザインを保存し,次に xdc ファイルを開きます.

MDIO と RGMII の配置を追加した状態に書き換えてください.

#UART

set_property PACKAGE_PIN R18 [get_ports uart_rtl_rxd]

set_property PACKAGE_PIN T18 [get_ports uart_rtl_txd]

set_property IOSTANDARD LVCMOS33 [get_ports uart_rtl_rxd]

set_property IOSTANDARD LVCMOS33 [get_ports uart_rtl_txd]

#QSPI

set_property IOSTANDARD LVCMOS33 [get_ports spi_rtl_io0_io]

set_property IOSTANDARD LVCMOS33 [get_ports spi_rtl_io1_io]

set_property IOSTANDARD LVCMOS33 [get_ports spi_rtl_io2_io]

set_property IOSTANDARD LVCMOS33 [get_ports spi_rtl_io3_io]

set_property IOSTANDARD LVCMOS33 [get_ports {spi_rtl_ss_io[0]}]

set_property PACKAGE_PIN P22 [get_ports spi_rtl_io0_io]

set_property PACKAGE_PIN R22 [get_ports spi_rtl_io1_io]

set_property PACKAGE_PIN P21 [get_ports spi_rtl_io2_io]

set_property PACKAGE_PIN R21 [get_ports spi_rtl_io3_io]

set_property PACKAGE_PIN T19 [get_ports {spi_rtl_ss_io[0]}]

#MDIO

set_property PACKAGE_PIN AA10 [get_ports MDIO_mdc]

set_property PACKAGE_PIN AB10 [get_ports MDIO_mdio_io]

set_property IOSTANDARD LVCMOS33 [get_ports MDIO_mdc]

set_property IOSTANDARD LVCMOS33 [get_ports MDIO_mdio_io]

#RGMII

set_property PACKAGE_PIN AA15 [get_ports {RGMII_0_rd[0]}]

set_property PACKAGE_PIN AB15 [get_ports {RGMII_0_rd[1]}]

set_property PACKAGE_PIN Y13 [get_ports {RGMII_0_rd[2]}]

set_property PACKAGE_PIN AA14 [get_ports {RGMII_0_rd[3]}]

set_property PACKAGE_PIN AA9 [get_ports RGMII_0_rx_ctl]

set_property PACKAGE_PIN Y11 [get_ports RGMII_0_rxc]

set_property PACKAGE_PIN Y16 [get_ports {RGMII_0_td[0]}]

set_property PACKAGE_PIN AA16 [get_ports {RGMII_0_td[1]}]

set_property PACKAGE_PIN AB16 [get_ports {RGMII_0_td[2]}]

set_property PACKAGE_PIN AB17 [get_ports {RGMII_0_td[3]}]

set_property PACKAGE_PIN AA13 [get_ports RGMII_0_tx_ctl]

set_property PACKAGE_PIN AB13 [get_ports RGMII_0_txc]

set_property PACKAGE_PIN U16 [get_ports RGMII_0_RESET_N]

set_property IOSTANDARD LVCMOS33 [get_ports {RGMII_0_rd[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {RGMII_0_rd[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {RGMII_0_rd[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {RGMII_0_rd[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports RGMII_0_rx_ctl]

set_property IOSTANDARD LVCMOS33 [get_ports RGMII_0_rxc]

set_property IOSTANDARD LVCMOS33 [get_ports {RGMII_0_td[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {RGMII_0_td[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {RGMII_0_td[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {RGMII_0_td[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports RGMII_0_tx_ctl]

set_property IOSTANDARD LVCMOS33 [get_ports RGMII_0_txc]

set_property IOSTANDARD LVCMOS33 [get_ports RGMII_0_RESET_N]

書き換えたら保存をして bit ファイルを生成します.

生成したら忘れずにメニューバーから File->Export->Export Hardware で

ハードウェアファイルを生成します.

include bitstream にしておき最後まで進めます.

ソフトウェア上の作業

PetaLinux を使用するためのおまじないを実行.

(UG1144では/opt/pkg以下で説明されているので適時環境に応じて変更してください)

source /opt/petalinux/2020.1/settings.sh

ディレクトリを ~/Project/linuxprj/sw まで移動します.

先程生成した bit ファイルを設定するためにコンフィグコマンドを実行します.

petalinux-config --get-hw-description=../

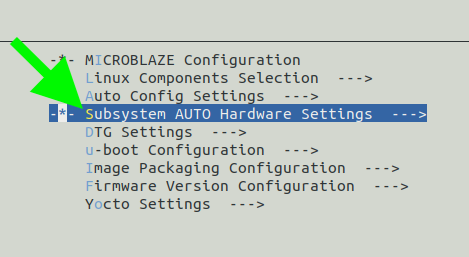

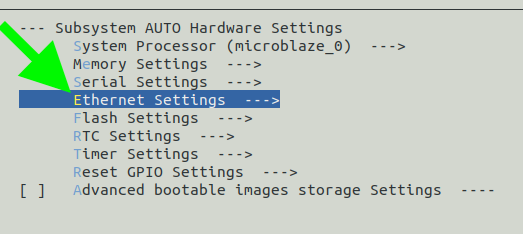

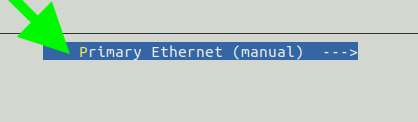

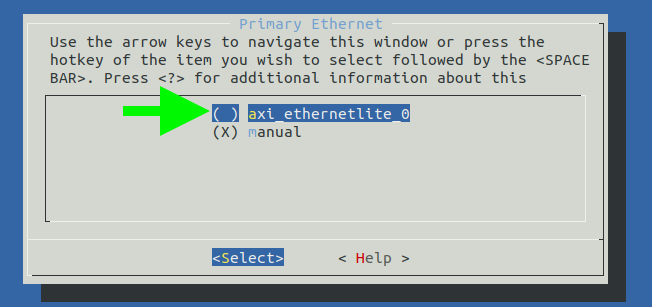

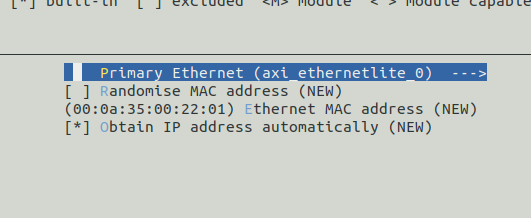

設定用のダイアログが開くので追加した Ethernet についての設定を行います.

Subsystem AUTO Hardware Settings->Ethernet Settings->Primary Ethernet

manual となっているところを axi_ethernetlite_0 に変更します.

保存して終了します.

次にビルドします.時間がかかります.

petalinux-build

ビルドが終わればソフトウェアは完成です.

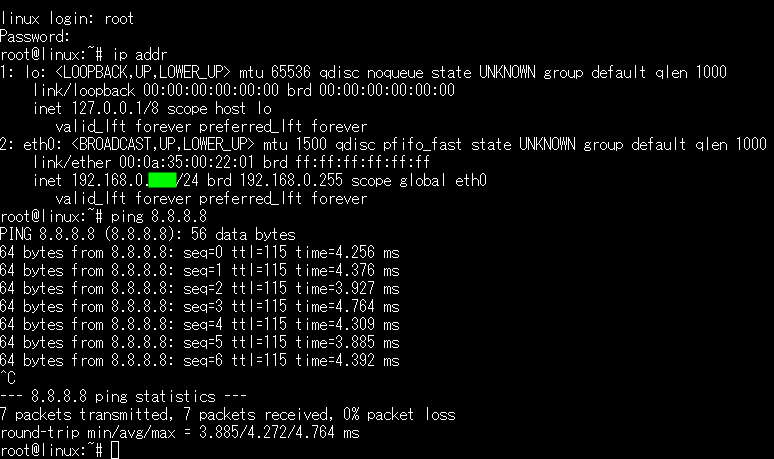

動かしてみる

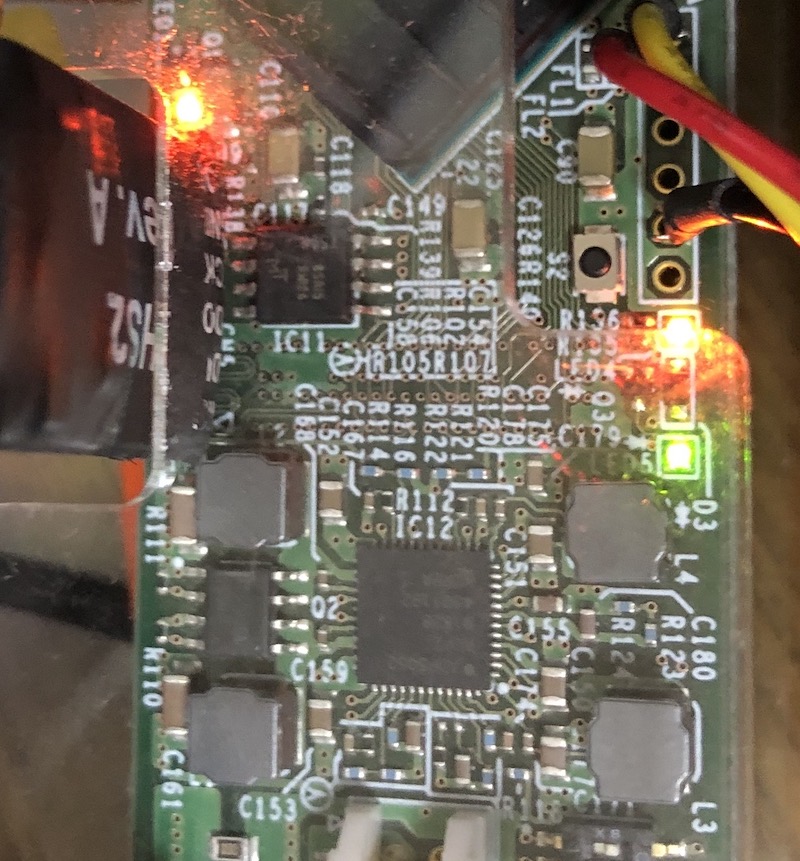

前回同様,動作確認をするためにシリアル通信モジュールを接続します.

FPGA側から見たピンアサインは 1:RXD ,2:TXD, 5:GND で IO レベルは 3.3V です.

JTAG ケーブルを接続し次のコマンドを実行します.

petalinux-boot --jtag --fpga petalinux-boot --jtag --kernel

そうすると FPGA にビットファイルが書き込まれメモリへ Linux が展開されます.

その後自動で走り始めるので待っているとログインプロンプトが表示されます.

ユーザ名及びパスワードはどちらも root です.

IPアドレスが確認でき, ping も通ることがわかります.

まとめ

前回のプロジェクトに追加する形で Ethernet IP を追加しました.

実際にインターネットへ通信することが確認できました.

FPGA 上で Linux が動作しインターネットに接続できることで更に用途が広がります.

追記: tftpboot に対応してみた

Microblaze 上で動かす Linux のデータをすべて JTAG 経由で書き込んでいましたが,

それだと時間がかかるのでネットワーク経由のブートもしてみました.

まずは tftp サーバを導入します.(ただし既にインストール&動作していました)

sudo apt install tftpd-hpa sudo systemctl start tftpd-hpa sudo systemctl status tftpd-hpa

既定のディレクトリは /var/lib/tftpboot でした.

sw プロジェクトにディレクトリ位置を指定します.

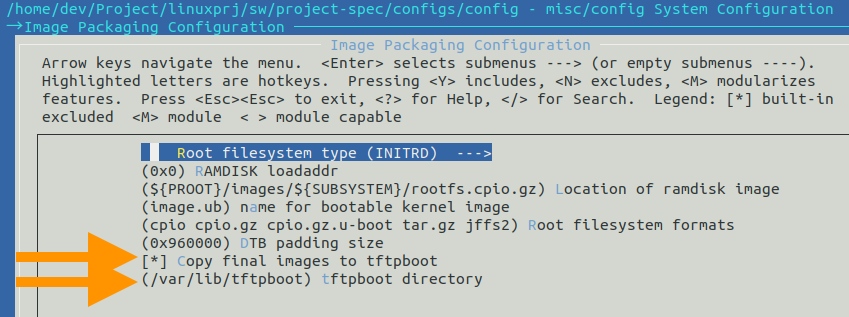

petalinux-config より Image Packing Configuration を開きます.

Copy final images to tftpboot にチェックが入っているかを確認し,

tftpboot directory に /var/lib/tftpboot を指定します.

保存をして抜けます.

ビルドをすると自動でディレクトリにコピーされます.

また,最低限最初に Microblaze 上で動かすソフトウェアもビルドします.

petalinux-build petalinux-package --prebuilt --force --fpga images/linux/system.bit

ここまでできればほとんど完成です.

ビットファイルと最低限のソフトウェアを転送します.

petalinux-boot --jtag --fpga petalinux-boot --jtag --prebuilt 2

ロードが終わるとシリアル通信モジュールから “Hit any key to stop autoboot” と

表示されるので適当なキーを押して自動ブートを止めます.

“printenv ipaddr” で IP アドレスが設定されているか確認し

問題なければ以下のコマンドを実行します.

必要なファイルをメモリ上にロードし,最後起動するコマンドです.

tftpboot 0x80000000 linux.bin.ub; tftpboot 0x81e00000 system.dtb; tftpboot 0x82e00000 rootfs.cpio.gz.u-boot;bootm 0x80000000 0x82e00000 0x81e00000;

この値は JTAG から起動したときの出力を参考にしています.

あとは以前と同じようにブートログが出力され

ログインプロンプトが表示されれば完了です.

JTAG からのブートに比べて速いので試してみてください.

コメント

[…] 前回はexStickGE上のMicroBlazeで動作するLinuxにEthernetを追加しました. ネットワークにつながったので今回はHTTPサーバを建ててみたいと思います. ついでにLEDのLチカを追加します.(ついでと言う割には作業量は結構増えます) […]