OpenCoresのSATAコントローラで遊んでみた,続・OpenCoresのSATAコントローラで遊んでみるから随分と時間が空いてしまいました.結局UART経由でホストPCからOpenCoresのSATAコア@ML605にアクセスしてみた,というところまでで,このお話は完結です.

このページでは,OpenCoresのSATAコアで遊んでみたの完結編として,FPGAマガジンNo.4に書かせていただいた記事に利用したリソース一式を紹介します.

OpenCores.orgのSATAコアについては,Serial ATA Host Bus Adapter Core for Virtex 6 :: Overviewをご覧ください.

記事には書いているのですが,結局安定的な動作をさせることができておらず,いまいちすっきりしないのですが,OOBから同期とるところまでをどんな感じでやり取りするか,とか,スクランブル/デスクランプル前後でデータがどうなっているか,とかを,実ディスクで試すことはよかったなあ,と.…負け惜しみに聞こえますか?…はい,負け惜しみです.

ちなみに,イーツリーズでは,e7SATA IPコアを新たにリリース,現在開発ボード上でのデバッグ,評価を進めているところです.作業が進み次第,また,ご連絡させていただければと思っています.

…私も早くアプリを作りたい.

これは何?

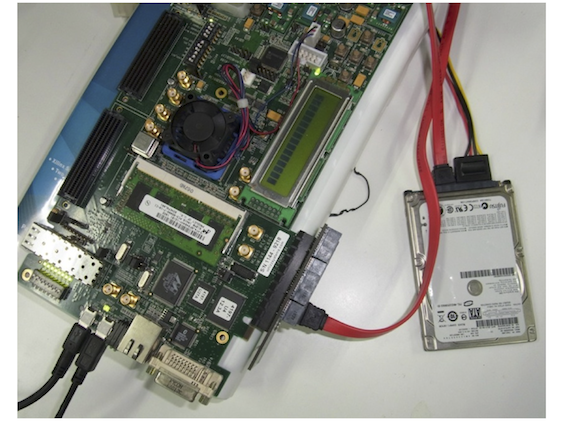

OpenCoresのSATAコアの動作をみてみるために,UART経由で簡単なアクセスができるフロントエンドを追加したリソース一式です.MicroBlazeな環境を構築するより楽なのでは,と思って実装しました.今振り返れば,MicroBlaze環境をちゃんと用意する方がよかったかも.

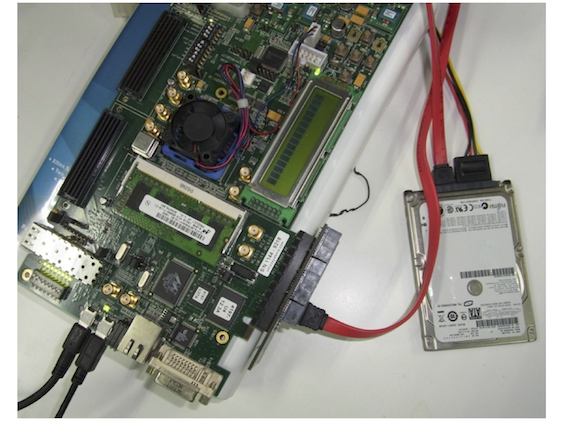

OpenCoresでSATAコアを作っている人たちとは違い,デザインゲートウェイさんのPCIeエッジとSATAコネクタを変換するアダプタ経由でディスクに接続しています.

リソース一式

- satacore_test_ml605.xise ISE14.x用のプロジェクトファイル

- source HDLソースコード一式

- software シリアル経由でFPGAとコマンドをやり取りするCプログラム一式

階層的には,

- sata_test_top

- U:sata_core SATAコア.OpenCores.orgで公開されているコードのコピー

- U_CTRL:simple_controller 適当に用意したSATAコアをたたくためのフロントエンド

- U_TX/U_RX:rs232c_tx/rs232c_rx UART回路

という,いたってシンプルなものです.

合成時には,CoreGenでFIFOやDCMを生成するプロセスが走ります.

使い方

“使い方”をわざわざ説明するほどのことはできませんが,FPGA内部のSATAコアにコマンドを送って,その結果を確認したり,カウンタの値を読んだりすることができます.合成時にChipscopeで見たい信号のプローブ作っておけば,内部の信号のやり取りを確認することもできますね.

実行は,LinuxやMacOSXの他,Windows上のCygwinで確認しています.Windowsで実行する場合には,conf.shを実行してシリアルポートのモードを設定する必要があります.以下,makeしてできる実行バイナリの簡単な説明です.

- sata_read – SATAディスクからFPGA内のバッファに読み出し,そのデータをホストPC上で表示します.

- sata_write – データをFPGA内のバッファにセットし,そのデータをSATAディスクにデータを書き出します.

- sata_read_test – SATAディスクにランダムデータを書き,それを読み出すことで,読み書が正常であることをチェックします.

- sata_read_command – SATAディスクにDMAリードコマンドを発行します.

- sata_write_command – SATAディスクにDMAライトコマンドを発行します.

- get_sata_counter – FPGA内部でコマンドの実行サイクルをカウントしているカウンタを読み表示します.

実行の様子

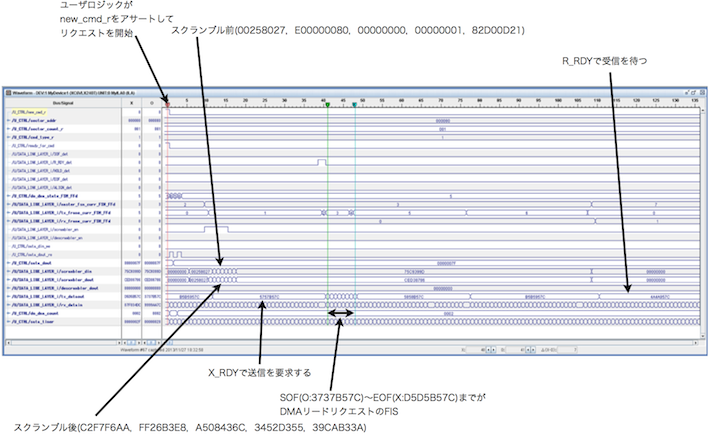

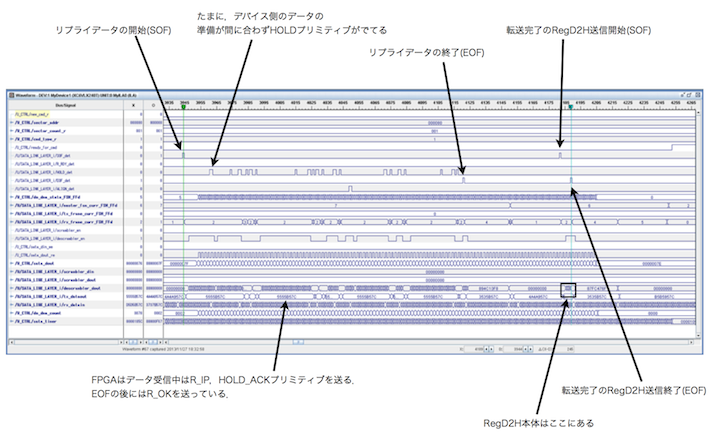

次のようなデータのやり取りを確認することができます.

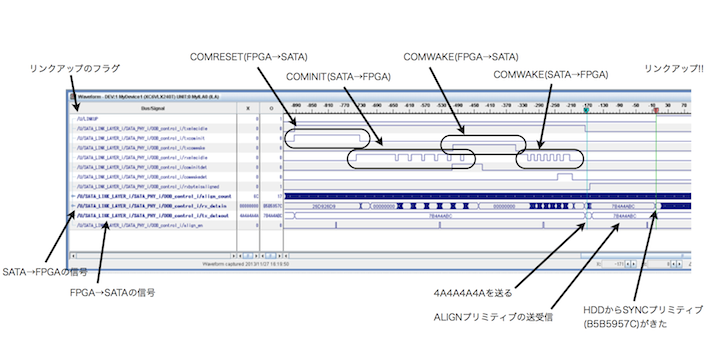

1. リンクが確立するまでのやり取り

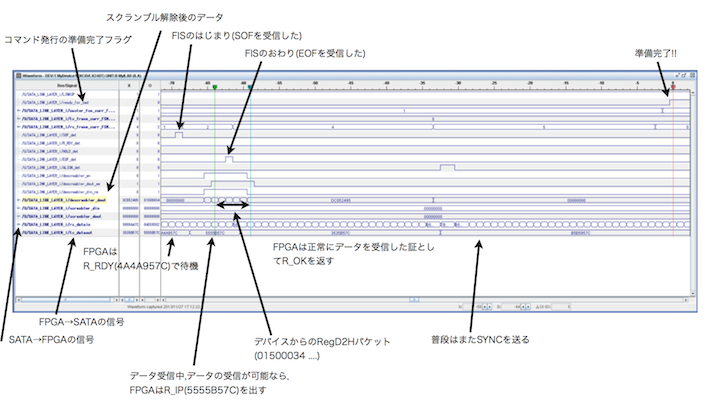

2. デバイス初期化完了パケットを受信するあたり

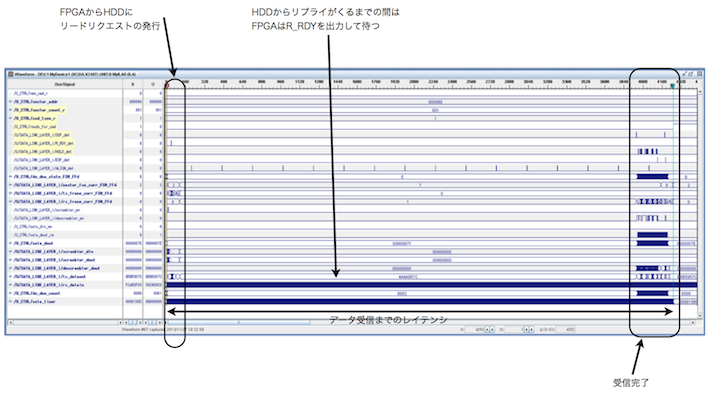

3. DMAリードリクエストとリプライの様子

4. 3のリクエスト部分を拡大してみたところ

5. 3のリプライ部分を拡大してみたところ

コメント