SATAは別ボードで気楽に使うAxfmc6040というアプローチがいいんじゃないかなーと思いながらも,ロジックをのせたFPGAから直接SATAにアクセスできる方が嬉しいというケースもあります.というわけで,2015年4月時点でまだまだコストパフォーマンスに優れている(個人の印象です)KC705にSATAをつないでみましょう.

Spartan6のGTPのコンフィギュレーションにはSATAプリセットが用意されていて便利だったのですが,Kintex-7のGTXのコンフィギュレーションにはSATAプリセットが用意されていません.というわけで,ドキュメント読みつつSpartan6のパラメタも参考にしつつパラメタを設定してみました.

この記事は現在試行錯誤中の内容につき,パラメタなど正しくない可能性があります.参考にされる場合は自己責任でお願いいたします.

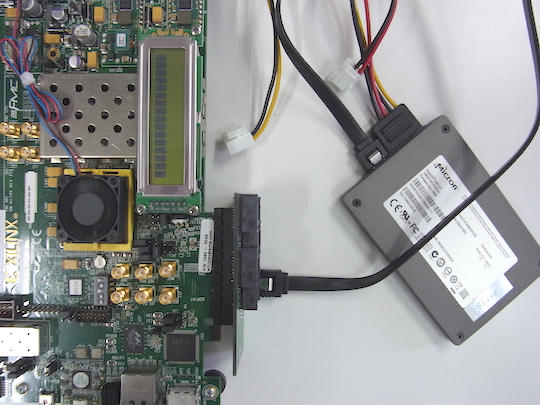

実験環境

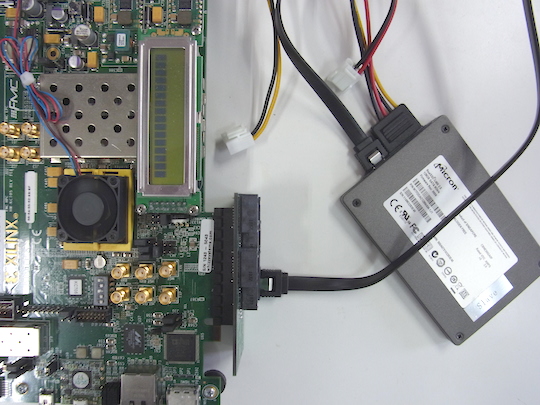

PCIeエッジをSATAコネクタに変換するデザインゲートウェイさんのアダプタを使って,KC705とSATAを接続しました.

コンポーネント図

コンポーネントは,こんな感じです(あとで書く)

クロックは,オンボードの200MHzオシレータの出力をCPLLのREFCLOCKに直接供給(IBUFDSだけを経由)し,GTXのTXOUTPUTCLKからでてきたものを300MHz,150MHz,75MHzに変換して使いました.

GTXのコンフィギュレーション

一般人の味方,CoreGeneratorで作成します.冒頭にも書いた通り,SATA用のプリセットがないので,自分でパラメタを入力していきます.ちなみに,sata_gtxという名前をつけました.ウィザードは1/7〜7/7までの7ページあります.

1/7

GTXしか選べないので,そのまま.

2/7

Protocol templateは”Start from scratch”を選択します.まずはGen2を試すことにして,Line Rateを3Gbpsに設定.リファレンスクロックは供給する200MHzを指定します.PLLはChannel PLLを選びました.

3/7

TX/RXともに,データ幅 16Bits,Encoding 8B/10Bに設定.自動的に内部データ幅は20 Bitsになります.Enable TX Buffer/Enable RX Bufferはチェックをいれます(多分デフォルト).

4/7

RXCOMMA Alignmentはそのままに.Optional PortsでRXSLIDEとRXBYTEISALIGN,RXCOMMADETを有効にします.この辺りはSpartan6のGTPの設定を参考にしました.また,この画面で,Terminal and Equalizationの設定として,RX Terminaton Voltageを800mVに設定.

5/7

OOBの設定です.ここは,いろいろと変更.試行錯誤中なので不要なものもあるかもしれません.

- SATA COM sequenceはデフォルトのBurst/Idles=7/7のままでおいておきました.GTPの設定のときはTXのBurst=15,RXがBurst/Idles=4/4だったのだけど…

- “PCI Express Parameters”の”Transition Time”はSpartan6の設定を参考に,To P2=100,From P2=60,To/From Non P2=25に変更.”Optional Ports”では,RXSTATUS,COMINITDET,COMWAKEDET,TXCOMINIT,TXCOMWAKE,TXELECIDLEを有効にしました.

- “OOB signalling and PRBS”の”Use RX OOB Signal Detection”を有効に.

- GTPの設定ではClock correctionのシーケンスが有効だったので,同じように有効にします.”Use Clock Correction”のチェックを有効にし,シーケンス長を4に設定.

6/7

5/7で指定したClock correctionのシーケンスを指定.次の通り.

- 10111100, K Character

- 01001010

- 01001010

- 01111011

7/7

サマリです.TXUSRCLKは300MHz,TXUSRCLK2は150MHzなんじゃないかな…と思いますが,特に何もせず.”Generate”をクリックしてウィザードを完了します.

生成されたコードの修正

AR# 53364 に従って,RXCDR_CFGの値を設定します.CoreGenで生成した プロジェクトディレクトリ/ipcore_dir の下に,sata_gtx_gt.vhdというファイルの値を変更します.(sata_gtxはCoreGenでGTXラッパーのIPコアにつけた名前に由来しています)

リンクアップ・シーケンス

SATAの初期化シーケンスでGTXコアをたたいてあげます.こんな感じですね.

- OOB操作なCOMINIT→COMWAKE

- D10.2を送り

- 続いてALIGNを検出(D10.2-K28.5を送り合う)し

- 最後にSYNCが送りあう

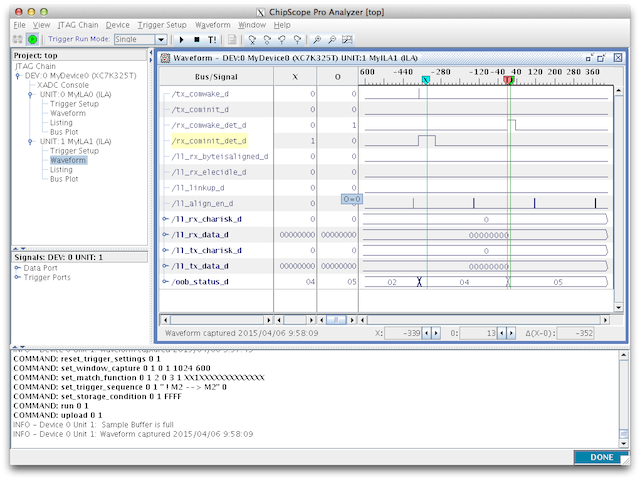

リンクがあがった?

というわけで,COMINIT→COMWAKE→ALIGNの検出→SYNCまでの一連の初期化が完了したところが次のスクリーンショットです.

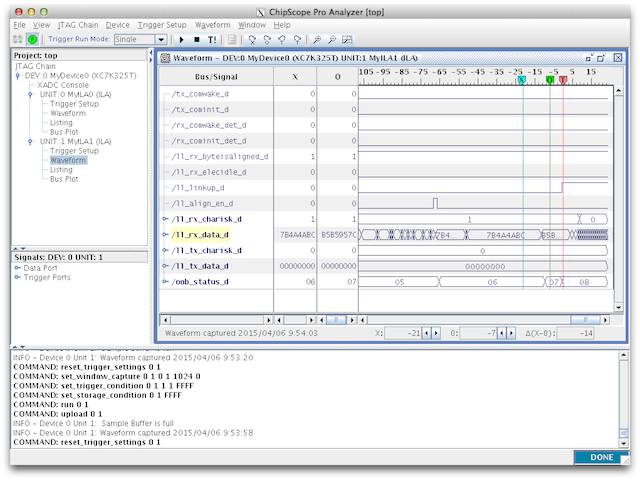

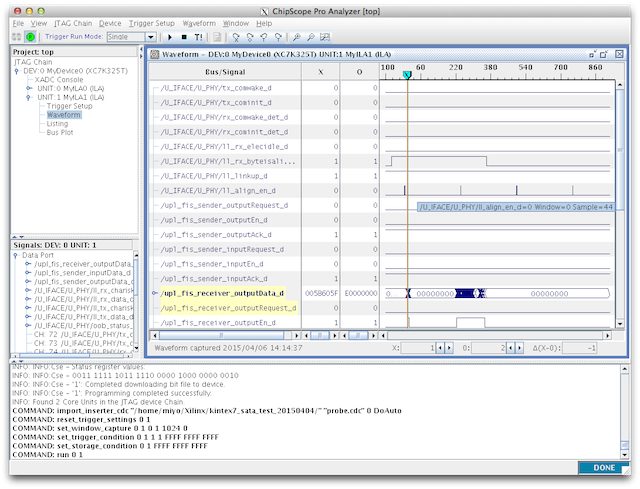

デバイスIDを読んでみる

リンクが確立できたので,以前開発したSATAコアの上位層とつなぎこんで,デバイスIDを読んでみます.デバイスIDを読むFISは

| 0x00ec8027 |

| 0x00000000 |

| 0x00000000 |

| 0x00000000 |

| 0x00000000 |

ですね.で,読んでみたところ結果が下の写真.5F605800(のひっくり返った値)を先頭に,データが返ってきました.

コメント