Xilinx 社が提供する RFSoC ZCU111 評価キット には,複数の DAC および ADCを内蔵した FPGA が搭載されています.本記事では,2つの RFSoC ZCU111 評価キットを用いて,異なるボード上の DAC を同期させて波形を出力する方法について紹介します.

非同期的な DAC の動作

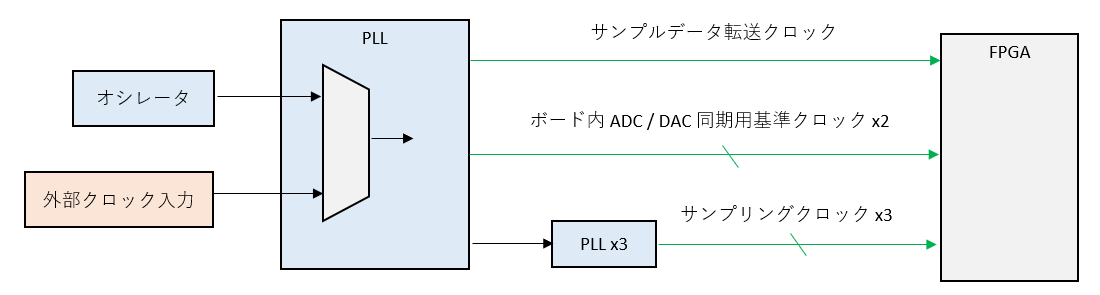

ZCU111 では,DAC と ADC の動作クロック (下図の緑の信号) は,ボード上のオシレータもしくはボード外部から入力したクロックから生成可能です.

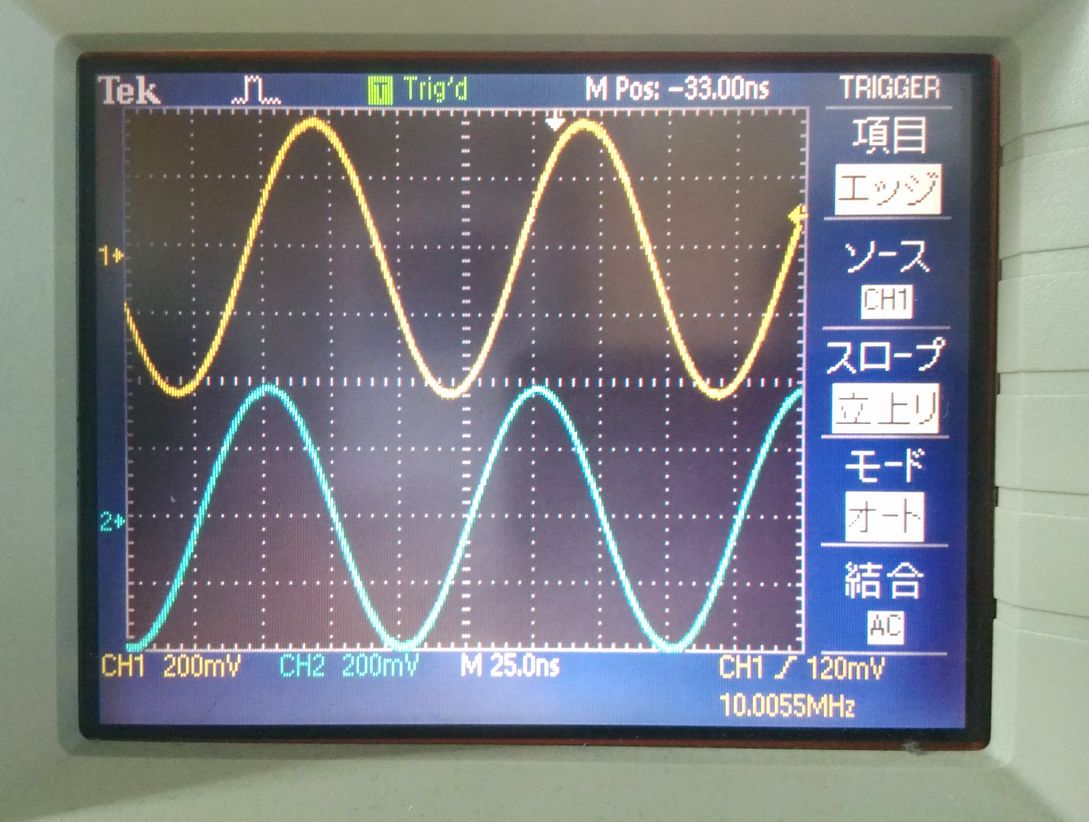

クロックソースとしてボード上のオシレータを用いた場合,各ボードのオシレータの揺らぎによって,異なるボード上の DAC および ADC が非同期的に動作します. このとき,2つのボードの同じ構成の DAC から同じ波形を出力したとしても,下の動画のように,時間が経つにつれて2つの波形の位相差が変化していきます.

共通のクロックソースを用いた DAC のボード間同期

このような位相差の変化を無くしたい場合,全てのボードで共通のクロックから,DAC および ADC の動作クロックを生成する必要があります. そこで,ZCU111 上の PLL の設定を変更し,ボード外部から入力したクロックからこれらの動作クロックを生成するようにします. 外部クロックは,シグナルジェネレータ (RIGOL DG2102) を使用して生成しました. FPGA 内部の回路構成は以下の通りです.

共通のクロックソースを使うことで,異なるボードの DAC から出力した 2つの波形の位相差が変化しないことが確認できました.

コメント