Xilinx 社が提供する RFSoC ZCU111 評価キット には、最大サンプリングレートが 4.096 [Gsps] [1] の A-D コンバータ (以下 ADC と記載) と6.554 [Gsps] の D-A コンバータ (以下 DAC と記載) が搭載されています。本記事では、この評価キットの ADC および DAC を最大サンプリングレートで動作させたときの回路構成や工夫した点などについて紹介します。

元にした回路

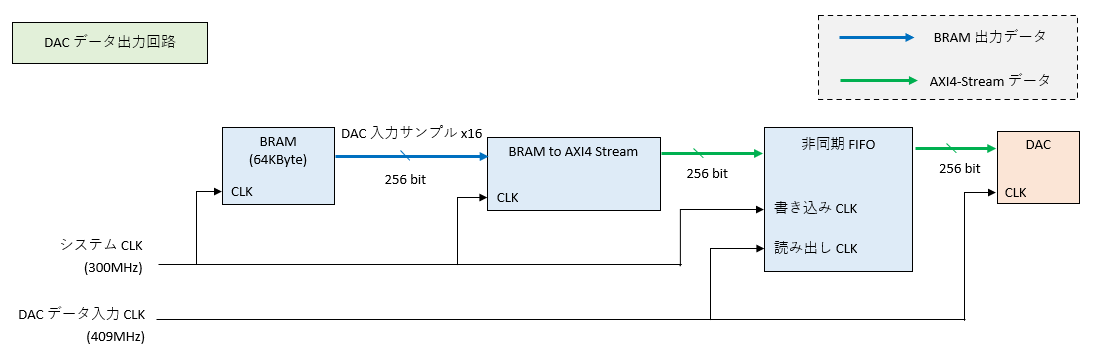

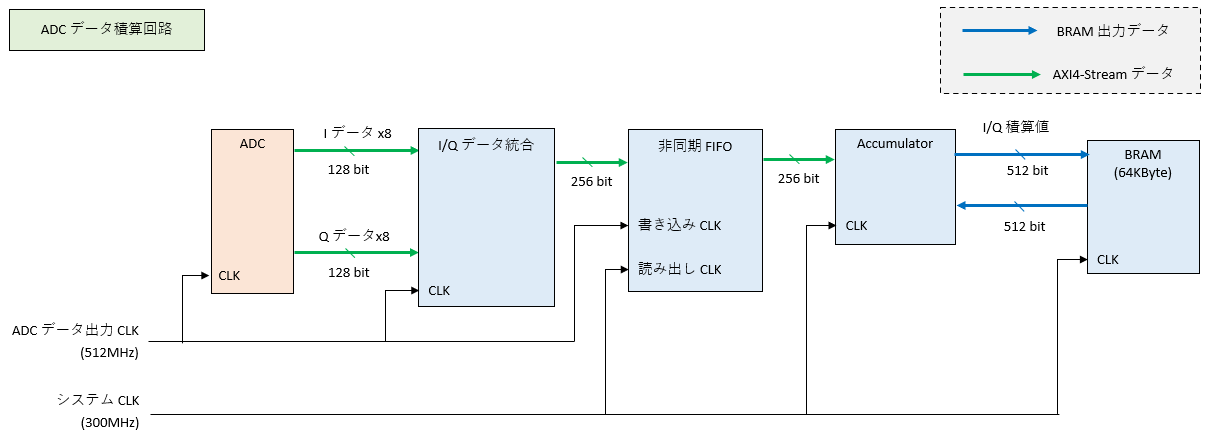

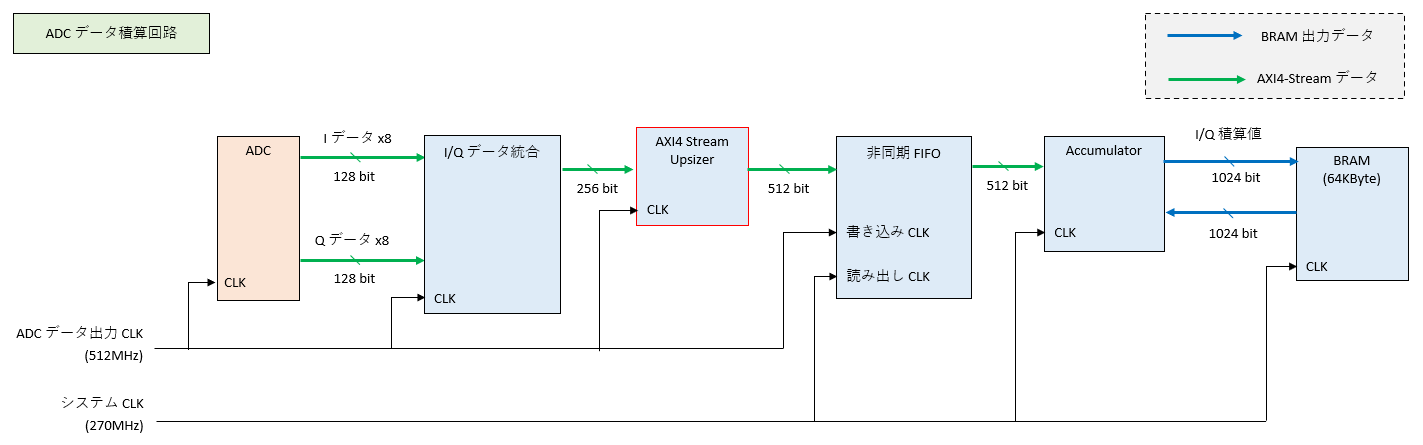

今回、最大サンプリングレートでの動作に挑戦するにあたって、以下に示す回路を改造しました。この回路は、元々、弊社で物理実験用に開発したもので、DAC データ出力回路は、BRAM に格納された波形データを一定の周期で繰り返し出力し、ADC データ積算回路は、一定の周期で取り込んだ波形データを、前回取り込んだデータとサンプルごとに足し合わせるという機能を持っています。

上図の回路の DAC および ADC のサンプリングレートは、BRAM のアクセス速度によって制限されており、それぞれ、対応可能なサンプリングレートは、以下の表の様になります。

| ADC / DAC | サンプリングレート [Gsps] |

|---|---|

| DAC | 4.8 [Gsps] |

| ADC (Realデータ) | 4.096 [Gsps] |

| ADC (I/Qデータ) | 2.4 [Gsps] |

表より、「DAC 波形出力回路」は最大サンプリングレートでは動作せず、「ADC データ積算回路」も I/Q データを扱う場合、最大サンプリングレートでは動作しないことがわかります。BRAM のアクセス速度を改善するには、「システム CLK」の周波数を上げれば良いのですが、ADC と DAC を最大サンプリングレートで動作させようとした場合、「DAC データ出力回路」では、410 [MHz]、「ADC データ積算回路」では、512 [MHz] 以上にする必要があります。試しに、両方とも 500 [MHz] にして回路を合成してみたところ、FPGA のタイミング制約を満たすことができませんでした。

修正した回路

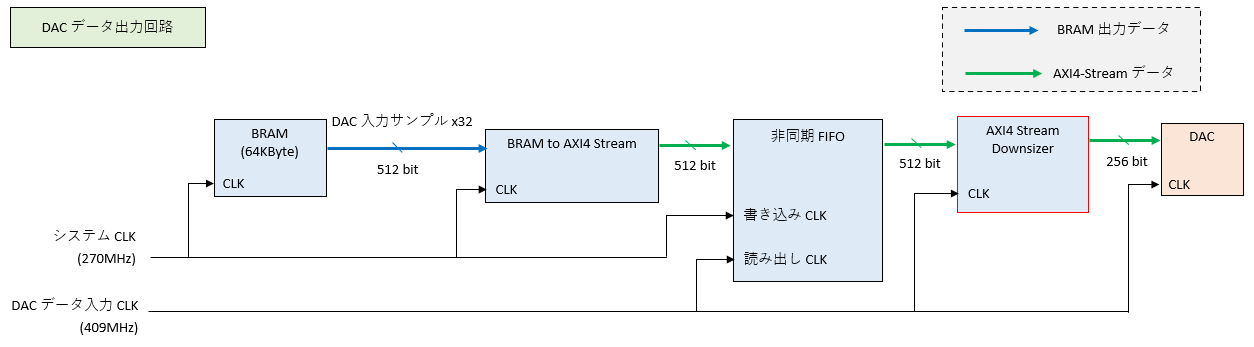

「システム CLK」の周波数は上げられないため、以下の図の様に、BRAM および積算回路のデータ幅を増やして、BRAM のアクセス速度を向上させました。この場合、最大サンプリングレートを達成するための「DAC データ出力回路」と「ADC データ積算回路」の「システム CLK」の最小周波数は、それぞれ、205 [MHz] と 256 [MHz] となります。DAC や ADC のインタフェースのデータ幅は、元の回路以上に広げることはできないため、修正後の回路には、これらのインタフェースと BRAM アクセス部分との間に、データ幅変換回路 (AXI Stream Upsizer と AXI Stream Downsizer) を挿入しています。

動作確認

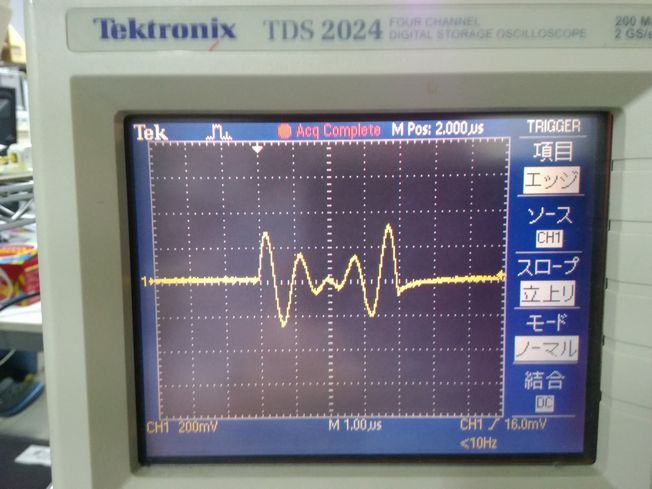

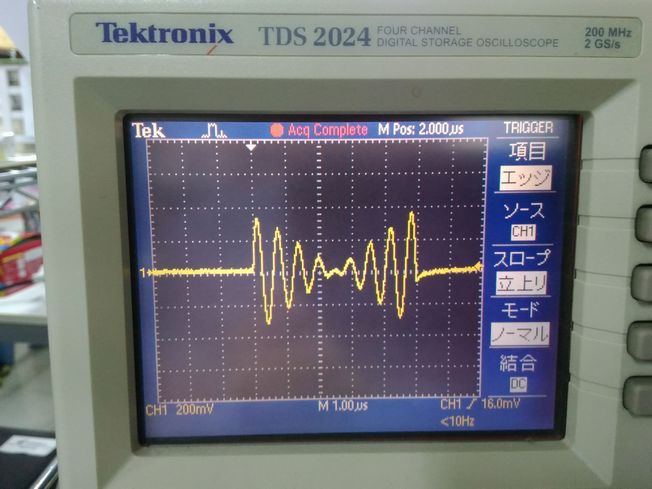

今回は、「システム CLK」を両方とも 270 [MHz] にして上図の回路を合成したところ、タイミング制約を満たすことができたので、動作確認をしてみました。 下の図は、BRAM に格納した 約 4.9 [μs] 分のデータ (32768サンプル) を、最大サンプリングレートに設定した DAC から出力させて、オシロスコープで波形を見たところです。 BRAM に格納した通りの波形が、4.9 [μs] で出力できていることが確認できたので、「DAC 波形出力回路」は正しく動作していると言えます。

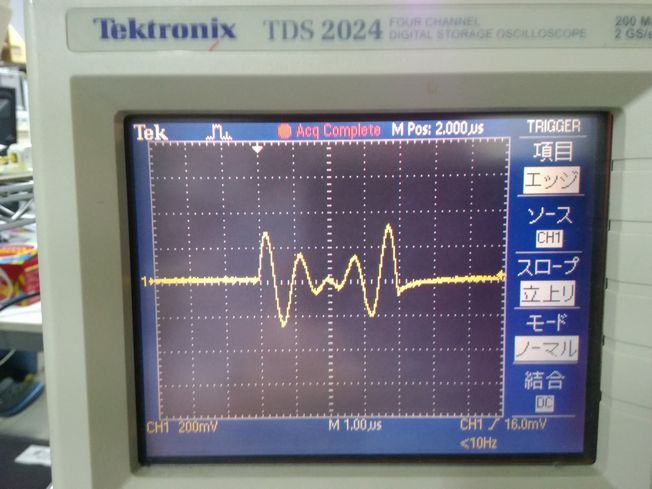

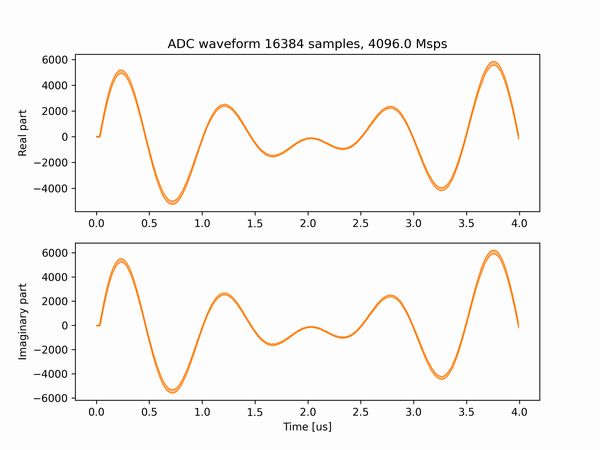

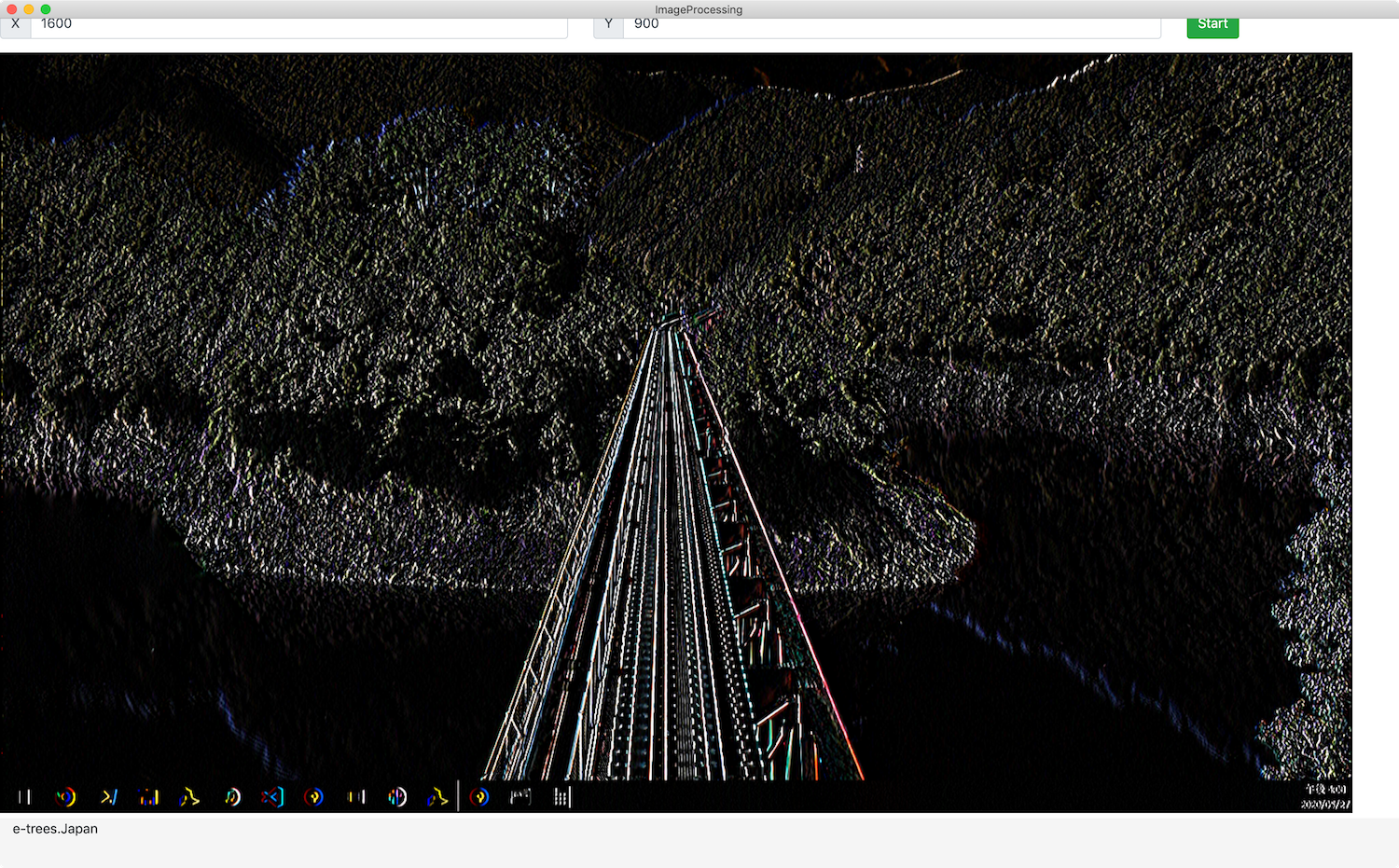

次の2つの図は、DAC から出力した 4 [μs] の波形と、それを最大サンプリングレートの ADC で取り込み、I/Q データとして BRAM に格納したものをソフトウェアで波形としてプロットしたものです (IとQ ともに取り込んだ波形をそのまま出力するように、Mixerを設定しています)。4 [μs] の波形が、欠けたり歪んだりすることなく取得できていることから、「ADC データ積算回路」も正しく動作していると言えます。 なお、積算処理は OFF にしています。

[1]Giga Samples Per Second

コメント