前回はexStickGE上でDDR3メモリを扱えるMicroBlazeを動かしたのですが

今回はAXI Ethernet Lite(以降Ethernet Lite)と呼ばれる無償のEthernetのIPコアをMicroblazeで制御させてみました.

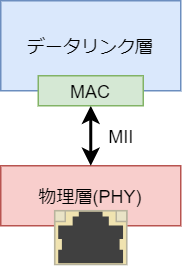

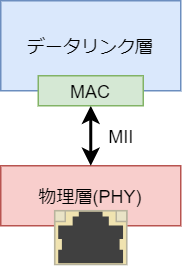

Ethernetのメディアアクセス制御(MAC)とPHYの関係

実際に動かす前にどうやってEthernetと接続するのかについて説明します.

普通はLANケーブルにつないで通信を行うわけですが, その通信を変換するための装置が

PHYでOSI参照モデルの物理層(L1)にあたるものです.

FPGA(に限らずほとんどのマイコンなど)では直接扱うことができません.

PHYチップと呼ばれる物理層の変換をする専用ICに物理層は任せ,

MACと呼ばれるデータリンク層(L2)の最下部を介してFPGAと通信します.

その間の通信を行うインターフェイスとして

media-independent interface(MII)が使用されます.

MIIは元々100MbpsのEthernet用でIEEE 802.3uで規定されています.

それを拡張して信号線を減らしたり1Gbpsでも使えるように

現在拡張されておりRMII, GMIIやRGMIIなどが存在します.

MIIはピンが送受信で15本使用されます.

| 送受信 | 信号 | 備考 |

| TX | クロック | 通信速度により可変 |

| TX | データ[4] | |

| TX | 有効 | |

| RX | クロック | 通信速度により可変 |

| RX | データ[4] | |

| RX | 有効 | |

| RX | エラー | |

| RX | キャリアセンス | 半二重モードのみ有効 |

| RX | 衝突検知 | 半二重モードのみ有効 |

RGMIIではピンが送受信で12本使用されます.

| 送受信 | 信号 | 備考 |

| TX | クロック | 通信速度により可変 |

| TX | データ[4] | |

| TX | 有効とエラー | クロック立ち上がりで有効, 立ち下がりでエラー |

| RX | クロック | 通信速度により可変 |

| RX | データ[4] | |

| RX | 有効とエラー | クロック立ち上がりで有効, 立ち下がりでエラー |

(どちらもクロックは10Mbpsのとき2.5MHz, 100Mbpsのとき25MHz, 1Gbpsのとき125MHz)

ところでEthernet Liteで使用されるインターフェイスはMII,

exStickGEに搭載されているPHYチップはRGMIIです.

exStickGEでEthernet Liteを使いたい場合は変換しなければなりません.

MIIとRGMIIの信号の違いはあまりなさそうにも見えます.

速度は100Mbps, 全二重通信と固定した上で進めます.

どちらも100Mbpsのときクロックは25MHzになるので,

お互いに接続すれば解決か, と思いきやそんなことはなく

RGMIIではデータの流れとクロックの供給は同じですが

MIIはどちらもMAC側から供給しなければならずうまく工夫しなければなりません

さらにクロックは受信時に位相をずらして使用する必要がありそれもまた大変です.

そのあたりのいざこざを解決するためのモジュールを作成したので

それを使えば一挙に解決です!

Ethernet LiteとexStickGEの組み合わせでしか検証していないので

その他の組み合わせのときはどうなるかはわかりませんが参考にはなると思います.

実際に動かしてみよう

今回もFPGA側のハードウェアとMicroBlaze上のソフトウェアに分けて作ります.

前回作成したプロジェクトを使用して作っていきますが

その前に新しいファイルを追加しなければいけないので以下のファイルが存在しなければ

gitでプルしてくるかここから以下のファイルをダウンロードして上書き, 追加しておきます.

- exStickGE_microblaze/sources/top.xdc

- exStickGE_microblaze/sources/mii2rgmii.v

FPGA側のプロジェクト

プロジェクトをVivadoで開きます.

まず新しいソースコードを追加します.

左上のAdd SourcesからAdd or create design sourcesで次へ

Add FilesでexStickGE_microblaze/sources/mii2rgmii.vを

選択してOK, Finishで追加します.

左上のOpen Block Designをクリックしブロックデザインを開きます.

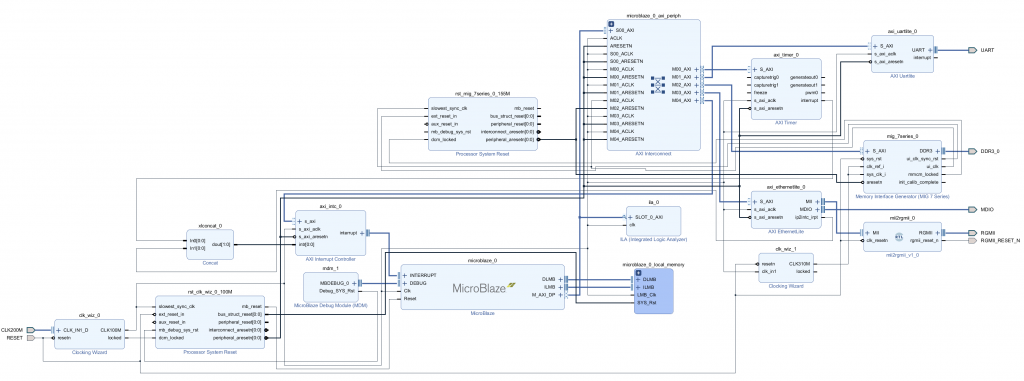

追加するIPは3つあります.

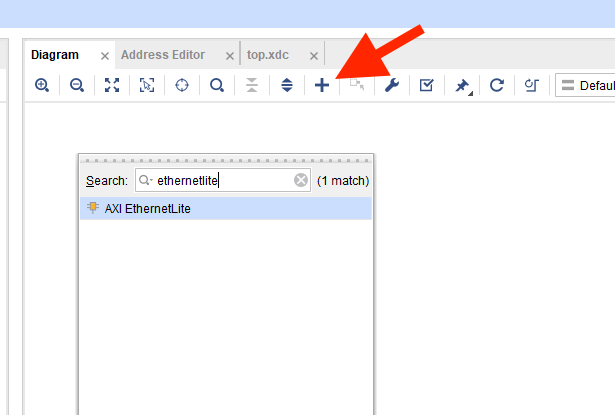

まず1つ目はメインのEthernet Liteです.

上の+からethernetliteを検索し追加します.

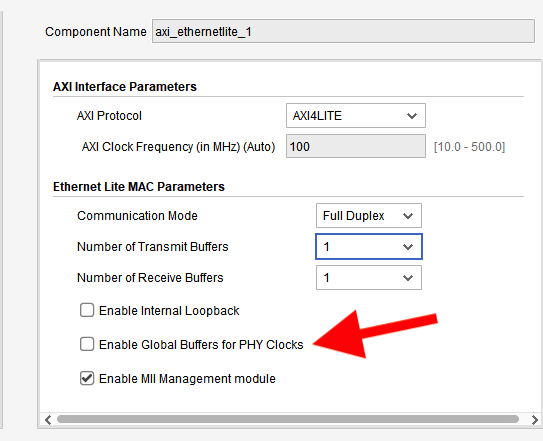

配置されたEthernet Liteをダブルクリックで設定画面を開きます.

Enable Global Buffers for PHY Clocksのチェックを外しOKをクリックします.

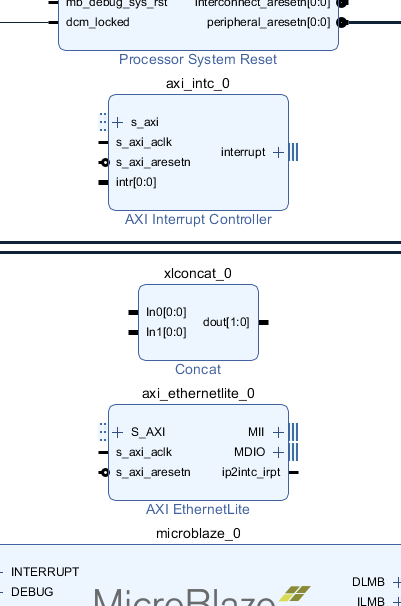

次に割り込み用のコントローラーを追加します.

+からAXI Interrupt Controllerを追加します.

割り込み信号をまとめるために結合用のIP Concatを追加します.

次に先程追加したソースコードをブロックデザイン内に呼び出します.

ブロックデザイン内の余白を右クリックでAdd Moduleでmii2rgmiiを選択します.

これで追加は終わりです.

次に配線していきます.

- Ethernet LiteのMIIからmii2rgmiiのMIIへ

- Ethernet Liteのip2intc_irptからConcatのIn1へ

- 左端のRESETからmii2rgmiiのclk_resetnへ

- AXI TimerのinterruptからConcatのIn0へ

- ConcatのdoutからInterrupt Controllerのintrへ

- Interrupt ControllerのInterruptからMicroBlazeのINTERRUPTへ

- mii2rgmiiのRGMIIを右クリックでMake External

- mii2rgmiiのrgmii_reset_nを右クリックでMake External

左上のRun Connection Automationをクリックして自動配線

All Automationにチェックを入れてOKで配線します.

ポートの名前を変更します.

- mdio_rtl_0をMDIOへ

- RGMII_0をRGMIIへ

- rgmii_reset_n_0をRGMII_RESET_Nへ

以上で完成です.

ただしこの状態ではMicroBlazeのメモリが足りなくこのあとのソフトウェアで詰まるので

容量を増やしてあげます.

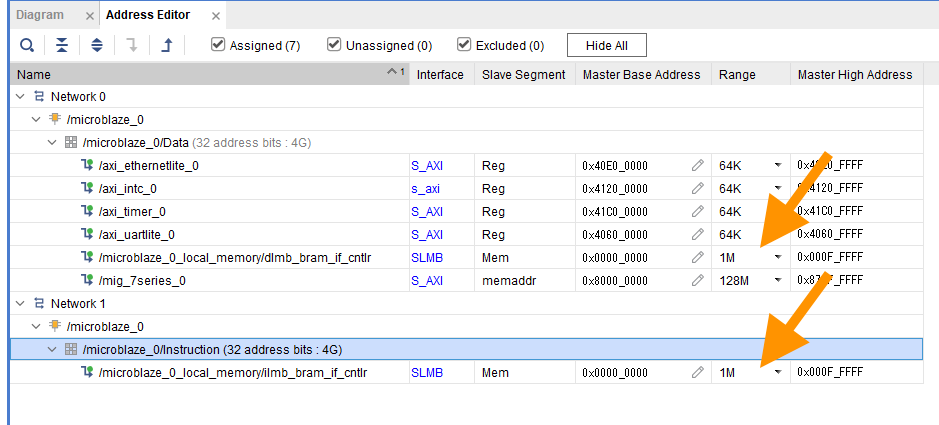

上のDiagramの隣Address Editorからdlmb_bram_if_cntlrとilmb_bram_if_cntlrの

容量をそれぞれ1MBに変更します.

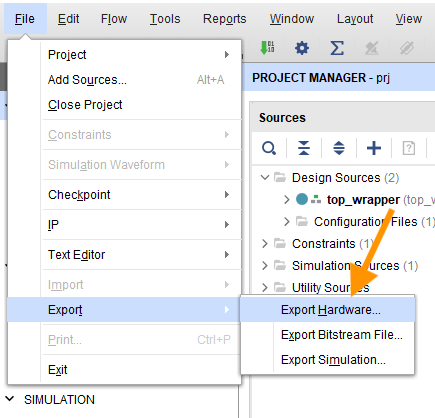

しっかりとセーブして左のGenerate Bitstreamからbitファイルを生成します.

bitファイルが生成されたら左上のメニューバーから

File->Export->Export Hardwareをクリック

前回と同様に

Platform typeはFixedで次へ, OutputはInclude bitstreamで次へ

Filesはそのままで次へ, Finishでxsaファイルが生成され完了です.

ソフトウェア側のプログラム

ソフトウェア側を作るためVitisを起動します.

ワークスペースは前回同様にprjフォルダ内のvitisフォルダを指定します.

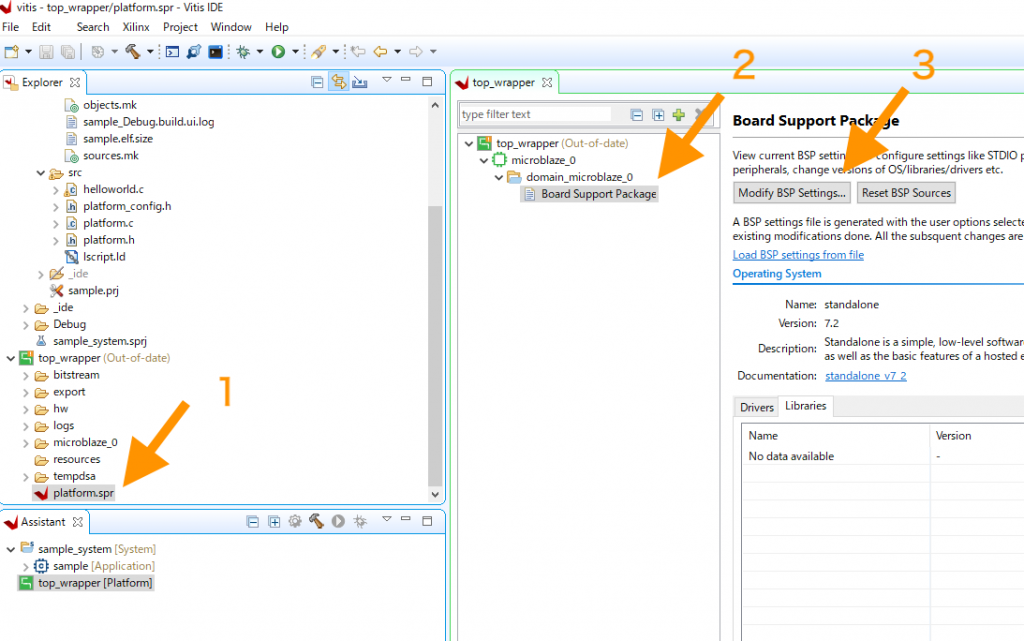

ハードウェア情報を反映

この状態では以前のVivadoプロジェクトの状態なので, 新しく生成したxsaファイルを

反映させて新しく追加したIPの情報やbitファイルを更新します.

左側にAssistantビューがあるのでその中のplatformプロジェクトのtop_wrapperを右クリック

まずCleanをクリックし自動生成されたものをきれいにします.

終わったら(Build Finishedと表示される)top_wrapperをまた右クリックし

Update Hardware Specificationをクリックしxsaファイルは既に設定されているので

そのままOKをクリックして内容を反映させます.

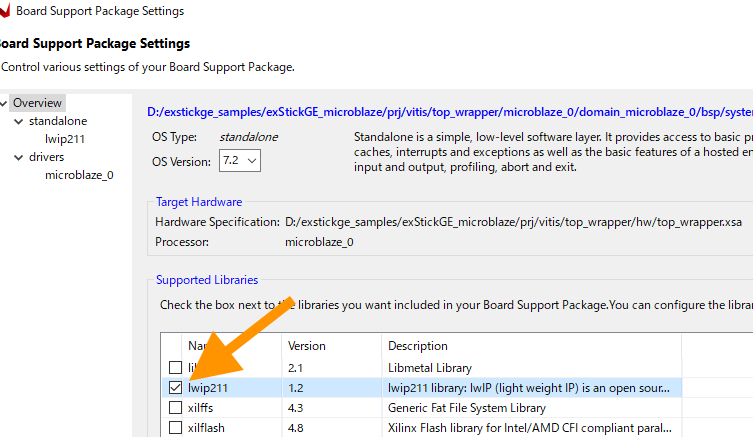

次に追加したEthernet Liteを使用するためのライブラリを追加します.

左のExplorerからtop_wrapper->platform.sprをダブルクリック

Modify BSP Settings…をクリックし設定画面を開きます.

Overview内のSupported Librariesからlwip211にチェックを入れます.

そうすると左のOverview->standalone->lwip211が増えるのでそれをクリック

temac_adapter_options->phy_link_speedを100Mbpsへ変更しOKで反映させます.

最後にtop_wrapperをまた右クリックしBuildをクリックして生成させれば

ハードウェア情報の反映は終了です.

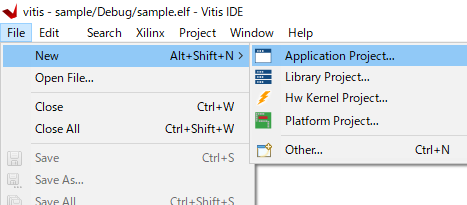

ソフトウェアプロジェクトを作成

前回はHello Worldテンプレートを使用しましたが今回はEcho Serverを使用します.

メニューバーからFile->New->Application Projectをクリック.

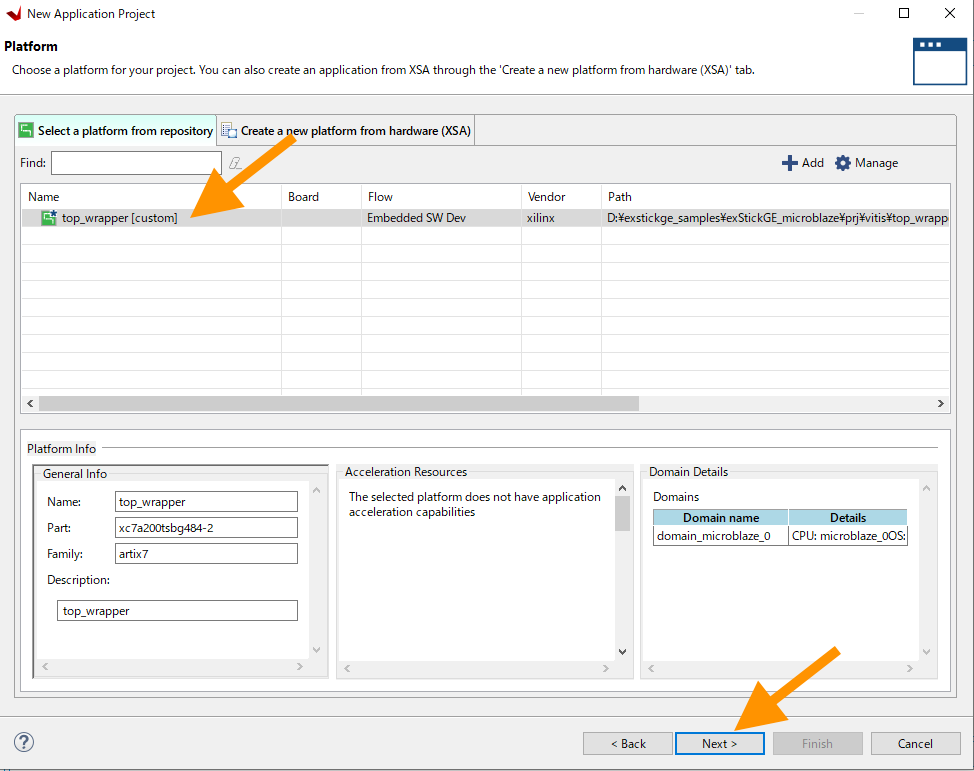

NextをクリックしPlatformではSelect a platform from repositoryで

既に存在するtop_wrapperを選択したままNext

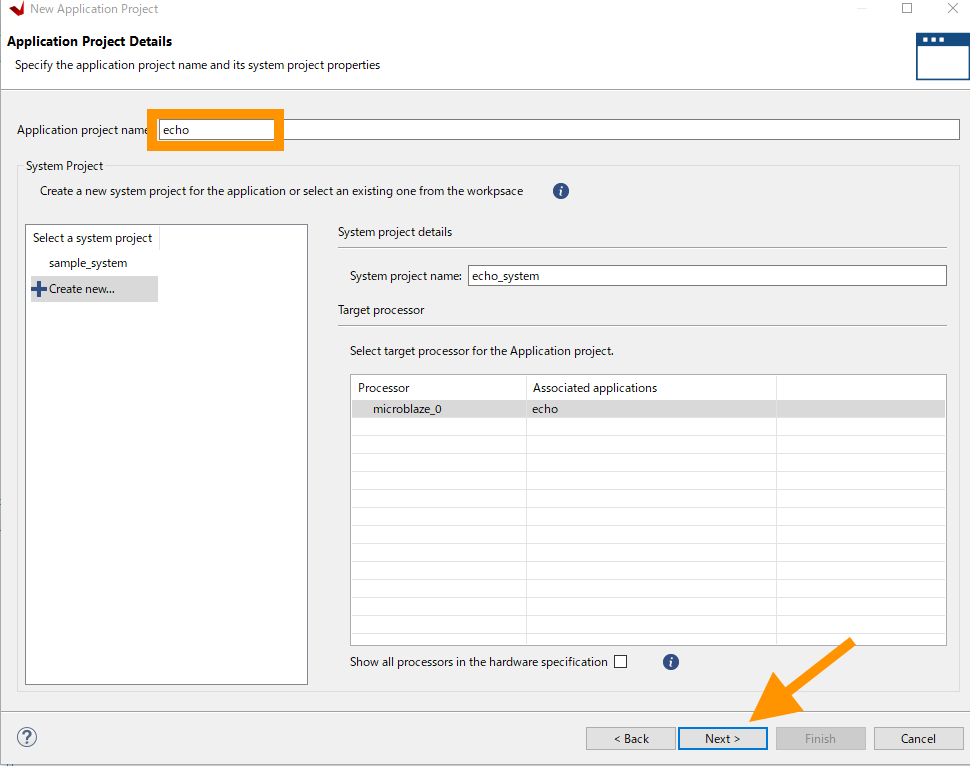

名前はechoとつけてNext

DomainはそのままNext

TemplateはlwIP Echo Serverを選択しFinish

プロジェクトが作成されます.

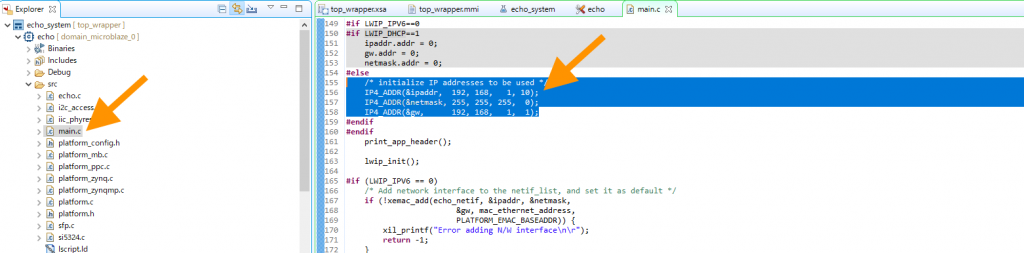

現状のままでは初期設定のIPアドレス192.168.1.10です.

必要に応じて変更します.

左のExplorerから作成したecho_systemを右クリック

Build Projectしてあげれば完成です.

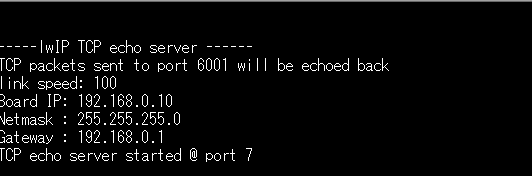

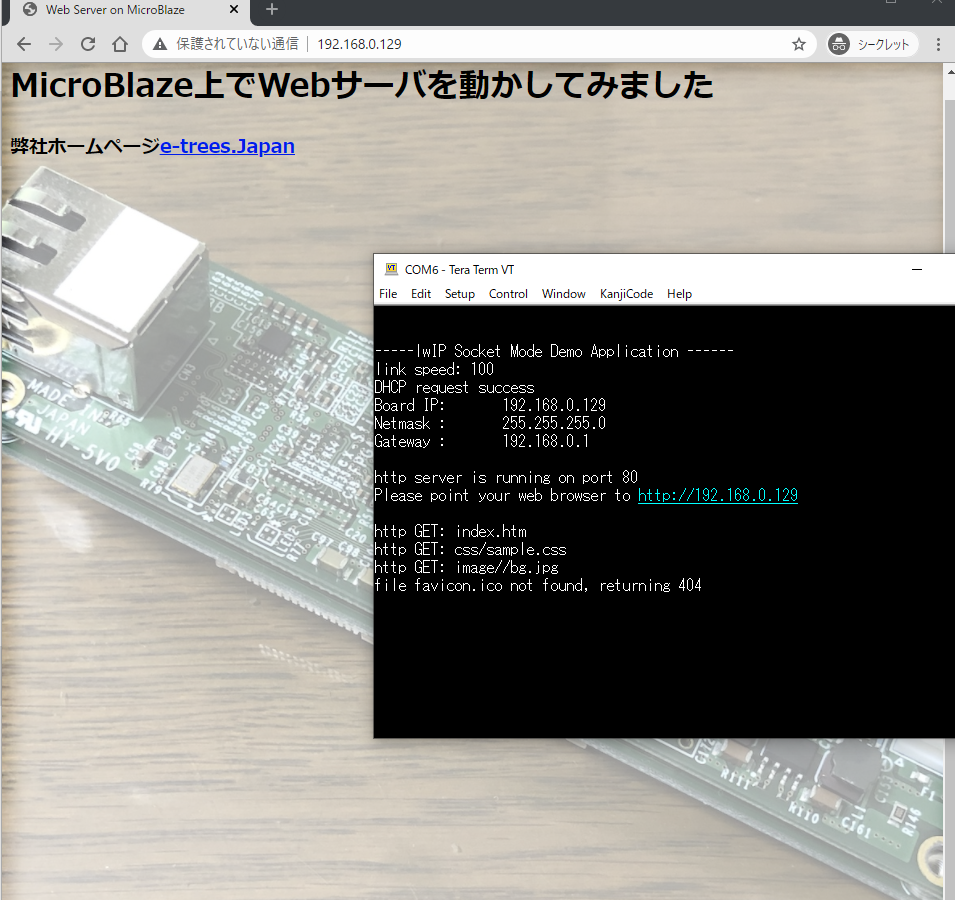

動作確認

実際に試してみましょう.

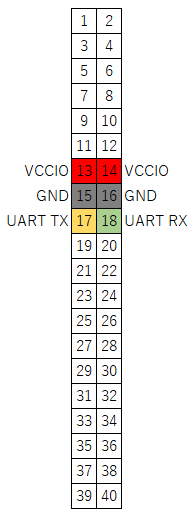

シリアル通信でIPアドレスの情報などが出てくるので, 前回同様接続します.

また今回はLANケーブルも接続します.

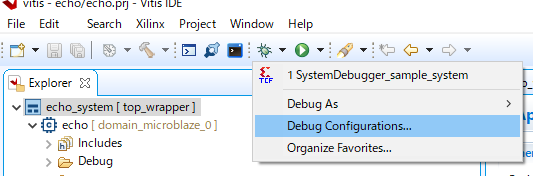

次に作成したecho_systemでデバッグするための設定を追加します.

上のバーから虫のマークの隣の黒い三角をクリックし,

Debug Configurations…をクリック.

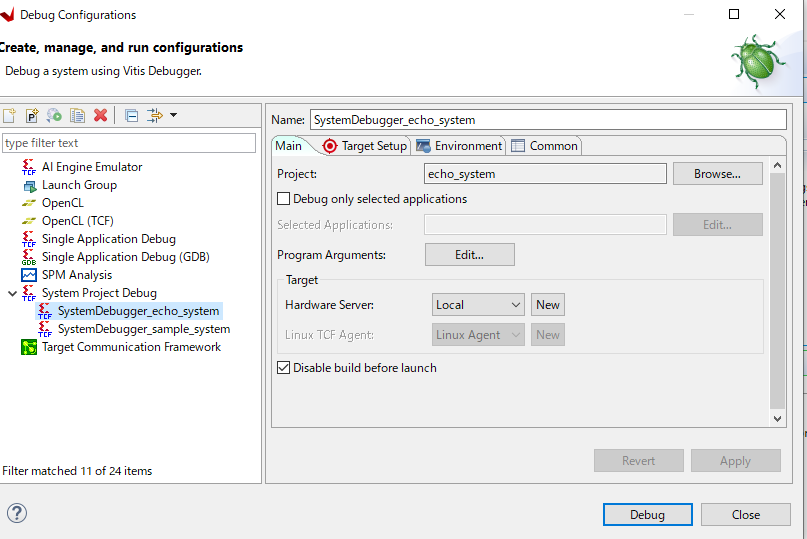

新しい設定を追加するため左のメニューからSystem Project Debugをダブルクリックします.

そうするとSystemDebugger_echo_systemが作成されます.

これで準備は完了です.右下のデバッグをクリックし開始します.

FPGAへデータが書き込まれ, MicroBlazeが動き始めます.

最初のエントリーポイントで停止するので上部のResumeボタンで再開します.

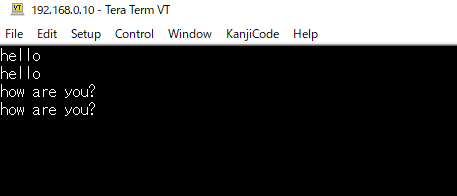

この情報に従いtelnetで接続します.

今回はTeraTermを使用しましたが, Setup->Terminalで

Local echoにチェックを入れるのと改行コードをLFにしないと見づらいです.

送信した結果がそのまま返ってくることが確認できました!!

さいごに

exStickGEを用いてEthernet Lite経由で通信することができました.

インターフェイスがMIIとRGMIIで違っているため, 適切に変換する必要があります.

その問題さえ解決すればかんたんに実装することができるため便利です.

Ethernetが使えると外部から制御できるので活用の幅が広がります.

コメント

[…] 前回はexStickGE上でEthernetのIPコアと連携しechoサーバを動かしました. […]

[…] 前回はexStickGE上でEthernetのIPコアと連携しechoサーバを動かしました. […]