あけましておめでとうございます.

さて年明け最初の,この記事では,タイトルの通りe7UDP/IPコアのレイテンシを測定してみた結果を紹介します.

結果だけ最初に書いてしまうと,”e7UDP/IPコア同士の対向でのループバック通信のレイテンシは,(1)最小では間欠的にパケットを送った場合にペイロード64Byteのパケットに対して7.2μ秒程度,(2)最大では全力でパケットを送った場合にペイロード1472Byteのパケットに対して180u秒程度でした”という話です.

1.測定環境

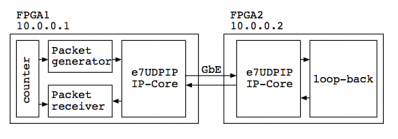

測定環境はこんな感じ.2枚のKC705(FPGA1とFPGA2)を用意して,イーサネットケーブルで直結しています.

特に変わったことはしていなくて

- FPGA 1はペイロードにカウンタの値をセットしたパケットを送る.

- FPGA 2は届いたパケットを送り返す.

- FPGA 1は送り返されたパケットのカウンタの値と,その時点のカウンタの値を比較する.

という単純なテスト環境です.

2.結果

測定結果は次のようになりました.レイテンシはだいたいの傾向をつかむべく,パケットの往復にかかった時間(ラウンドトリップタイム)を10回程度測定して平均した値です.送信レイテンシ・受信レイテンシは,およそ1/4した値になると思われます.パケット占有時間は,パケット長をスループットの125MBpsで割った値です.ラインレート1Gbpsに対して,パケットがあるモジュールを占有する時間に相当します.

FPGA0が送信間隔0で全力でパケットを生成・送信する時

| ペイロードバイト数 | トータルパケット占有長 | パケット占有時間(μ秒) | レイテンシ(μ秒) |

| 64 | 130 | 1.04 | 135.9 |

| 256 | 322 | 2.58 | 139.8 |

| 1024 | 1090 | 8.72 | 158.2 |

| 1472 | 1538 | 12.3 | 180.1 |

FPGA0が送信間隔14348サイクルでパケットを生成・送信する時

| ペイロードバイト数 | トータルパケット占有長 | パケット占有時間(μ秒) | レイテンシ(μ秒) |

| 64 | 130 | 1.04 | 7.2 |

| 256 | 322 | 2.58 | 16.8 |

| 1024 | 1090 | 8.72 | 53.2 |

| 1472 | 1538 | 12.3 | 74.7 |

全力でパケットを送る場合には,モジュール間のreq/ackの待機に伴ってバッファにパケットがたまるため,レイテンシが大きくなっていることがみてとれます.

また,この表にはあらわれていませんが,パケット間隔をあけている場合にはレイテンシのばらつきも小さいという傾向がみられました.

3.次は

正直,ここまでバッファの影響が見えるとは思っていなかったので,分散を含め,もう少しまじめに測定してみようかな,と思っています.

また,結果を踏まえた上で今後のコア開発を考えてみると,アプリケーションによってはQoSバッファの導入も必要かもしれませんね.

コメント