Vivadoにはボードファイルと呼ばれる機能があります.

この機能を使うとブロックデザインでぽちぽちポートを作成しそれに適したIPを別途生成する

作業が一度に完了し,xdcファイルによるポートの指定が必要なくなります.

Xilinx社のリファレンスボードやDigilent社の開発ボードにはボードファイルが

付属もしくは公開されているため簡単に使用することができます.

せっかくなので弊社のexSitckGE用のボードファイルを作成しました.

その使い方について解説します.

バージョンはVivado,Vitisどちらも2020.1です.

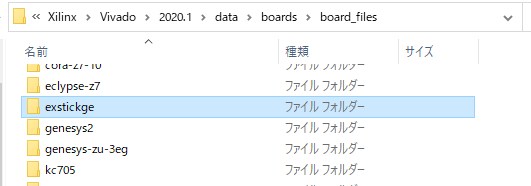

ボードファイルの追加

まずボードファイルを追加する必要があります.

GitHubのリポジトリからダウンロードします.

配置場所ですがWindowsで初期設定のインストール場所だと以下のフォルダです.

C:\Xilinx\Vivado\2020.1\data\boards\board_files

注意点はHDMI入出力はDigilent社のIPを使用する指定がしてあるので

別途リポジトリでIPが使えるようにしないといけません.

また,後述しますがDIPスイッチはそのまま使うことができないので

別途xdcファイルを指定する必要があります.

実際に使ってみる

ボードファイルが登録されたのでVivadoから使ってみます.

exStickGEでMicroBlazeを動かしLチカを試します.

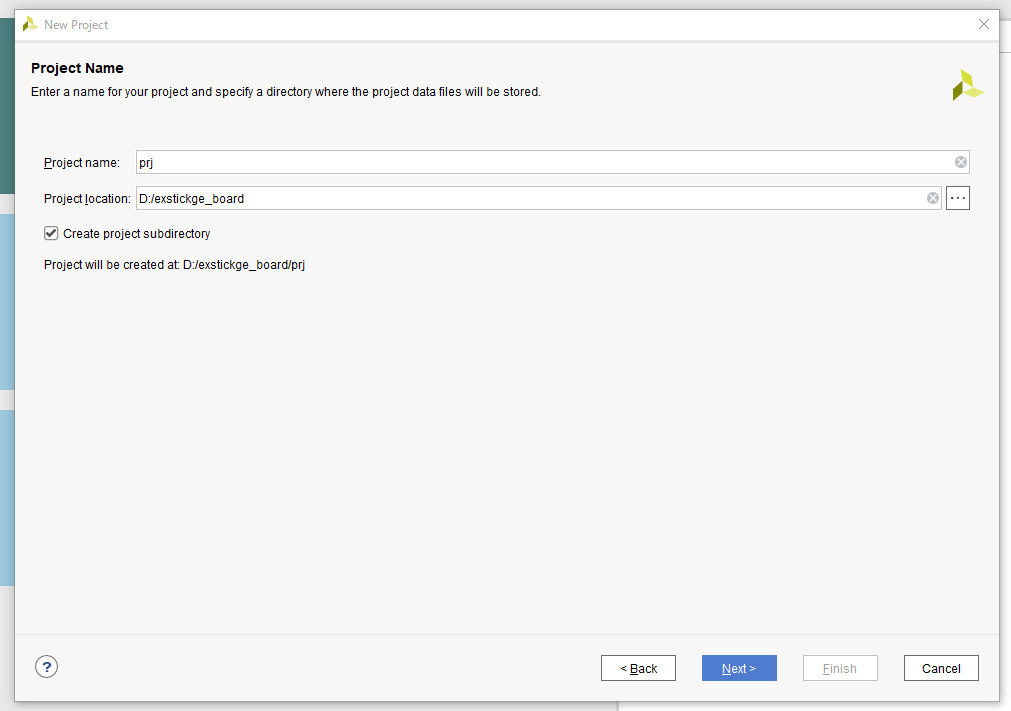

プロジェクトの作成

Vivadoから新プロジェクトの作成,適当な名前をつけます.

Add Constraintsまでそのまま進めます.

ボード上にDIPスイッチが存在するのですが,プルダウンしないと使えないので

別途xdcファイルで指定します.(今回は使う予定はありませんが)

リポジトリ内に”constraints.xdc”があるので追加します.

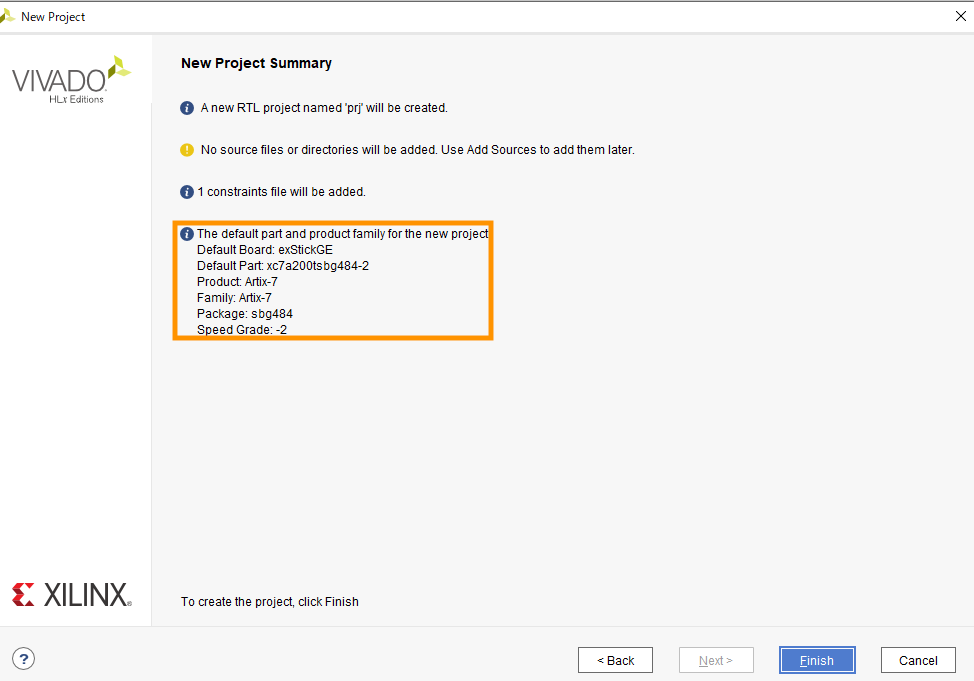

次にDefault Partで今回の目玉であるボードを指定します.

FPGAの種類xc7a200tsbga484をわざわざ探し出すことなく指定することができます.

exSitckGEが選択されているのを確認してFinishで完了です.

今回はシリアル通信の入出力は汎用ポートから行う予定で

ボードファイルには定義されていないので別途xdcファイルで指定します.

Sourcesから先程追加したxdcファイルに追記します.

以下の4行を追記してください.

set_property PACKAGE_PIN H22 [get_ports UART_rxd] set_property PACKAGE_PIN J22 [get_ports UART_txd] set_property IOSTANDARD LVCMOS33 [get_ports UART_rxd] set_property IOSTANDARD LVCMOS33 [get_ports UART_txd]

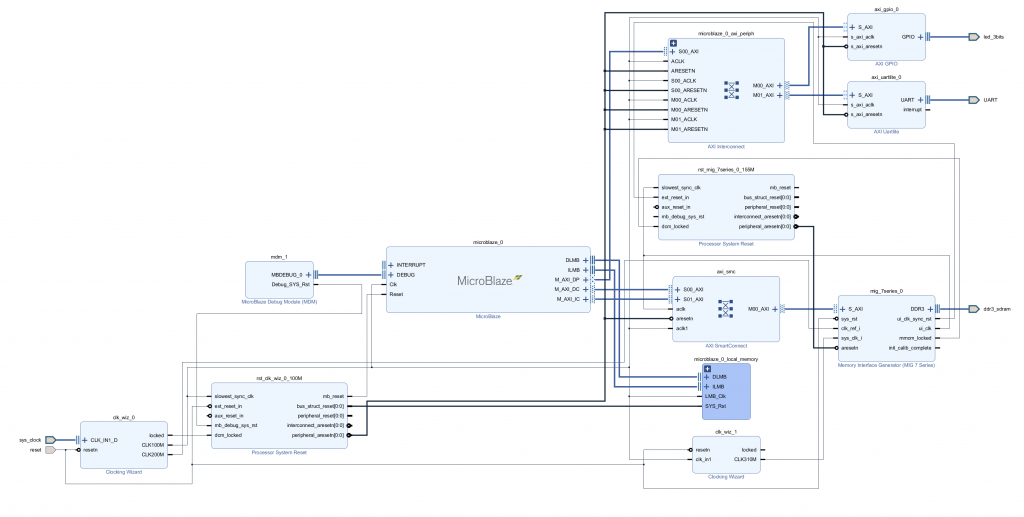

ブロックダイアグラムの作成

左のFlow NavigatorからCreate Block Designで作成します.

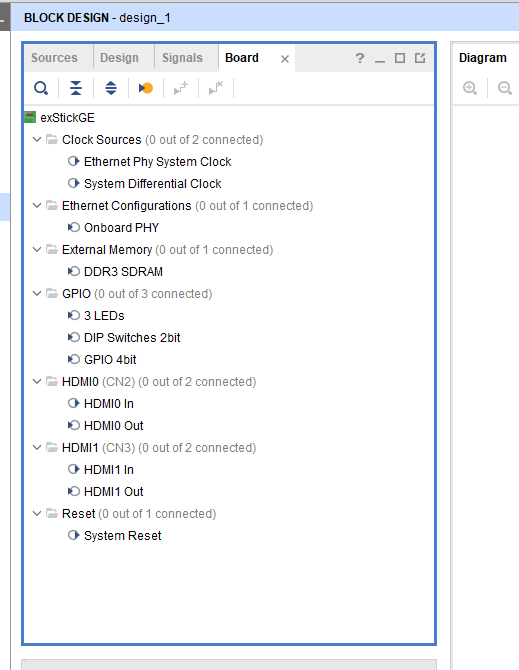

Boardタブから定義済みのインターフェイスが表示されます.

今回はexStickGEを生成するのでまずクロックから作っていきます.

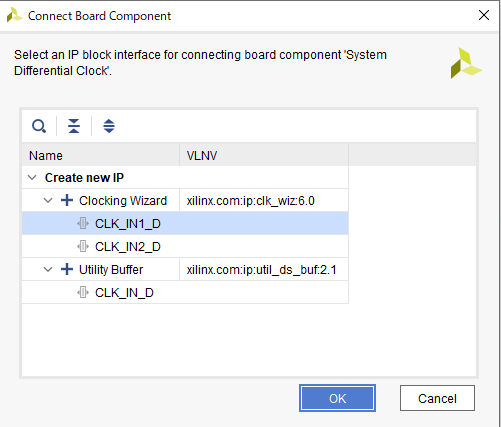

Clock Sources->System Differential Clockをダブルクリック

接続先IPの指定が出てくるのでCLK_IN1_Dが選択されたままOK

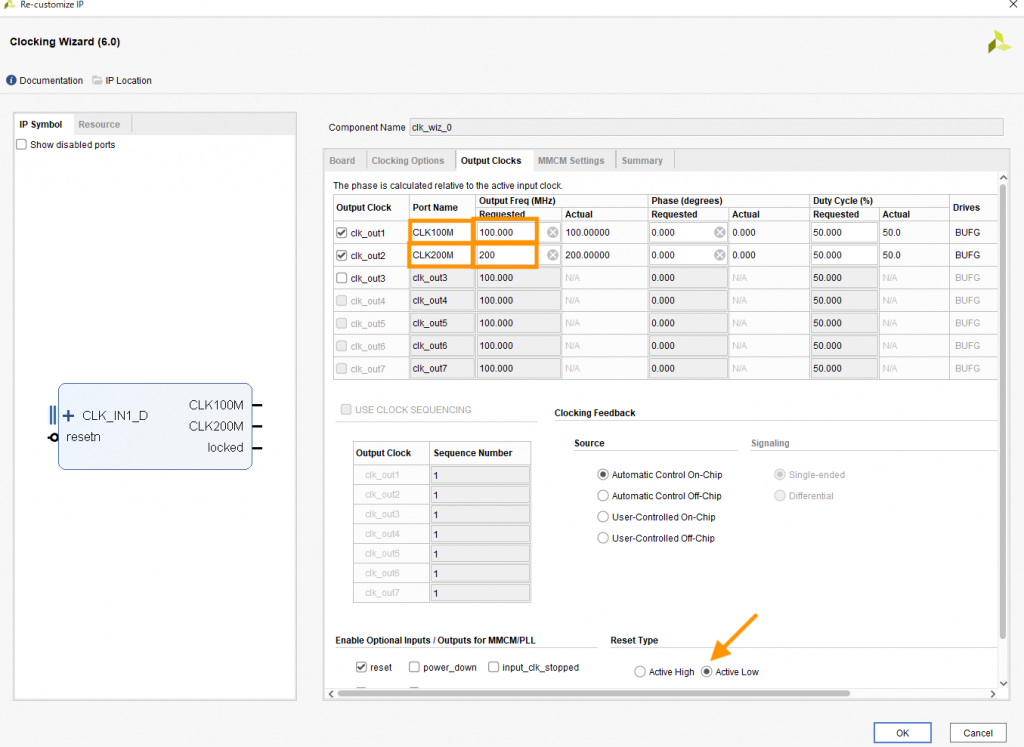

生成されたIPをダブルクリックして設定を変更します.

Output Clocksタブで以下のように変更します.

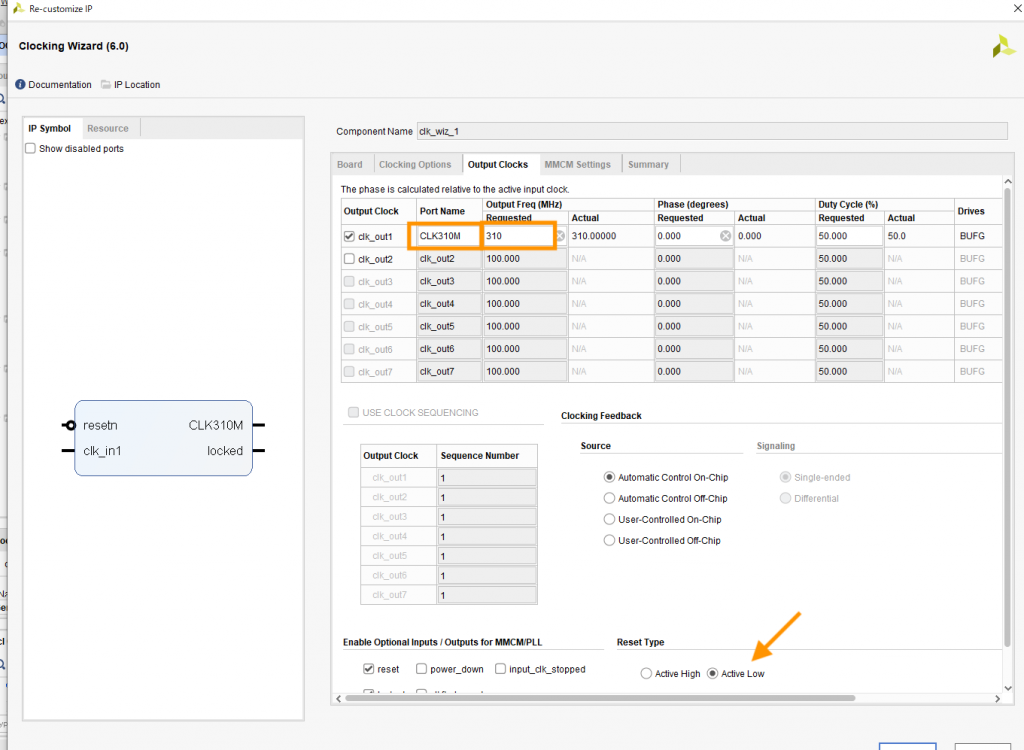

MIGを動かすためにAdd IPからClocking Wizardをもう一個追加します.

以下の設定に変更します.

次にMIGを追加します.

External Memory->DDR3 SDRAMをダブルクリック

そのままOKで作成します.

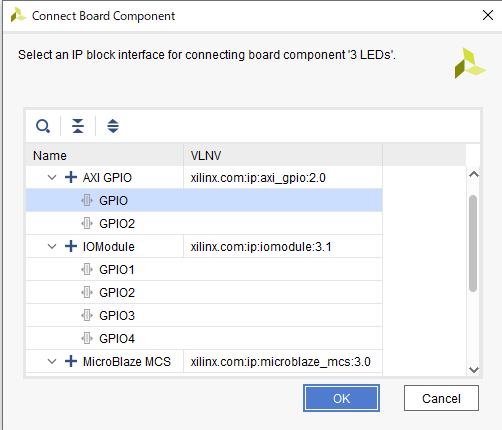

次にLEDを追加します.

GPIO->3 LEDsで作ります.

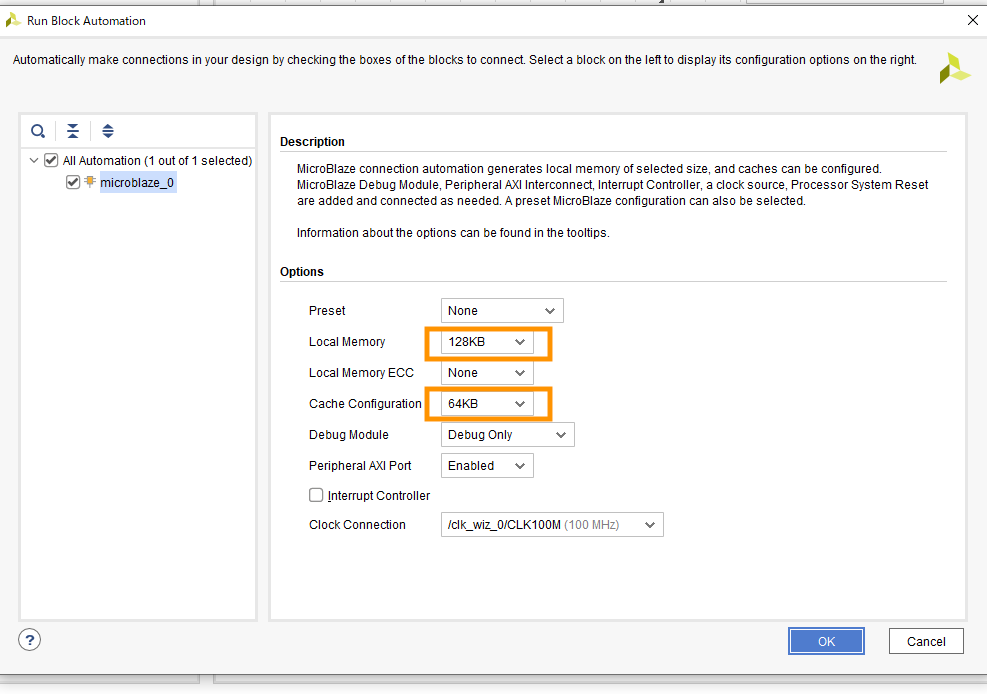

次はMicroBlazeです.

Add IPからMicroBlazeを追加,上部のRun Block Automatinをクリック

余裕があるのでローカルメモリを128KB,キャッシュを64KBにしておきます.

デバッグ用にシリアル通信モジュールも追加します.

Add IPからAXI Uartliteを追加します.

自動で生成されたUART入出力ピンはuart_rtlからUARTに名前を変更しておきます.

最後の追加はリセットです.

Reset->System Resetをダブルクリック

設定は以下の図のようにします.

最後に配線を調整します.

clk_wiz_1のclk_in1はclk_wiz0のCLK100Mへ

MIGに接続されているclk_ref_iとsys_clk_iのポートを削除

MIGのclk_ref_iはclk_wiz_0のCLK200Mへ

MIGのsys_clk_iはclk_wiz_1のCLK310Mへ

上部のRun Connection Automationをクリックし全てにチェックを入れOK

以下の画像が完成図です.

保存したら左のFlow NavigatorからPROJECT MANAGERに移動しSourcesから

ブロックデザインを右クリックし,Create HDL Wrapperをクリック

そのままOKをクリックし完成です.

Generate Bitstreamでビットファイルを生成します.

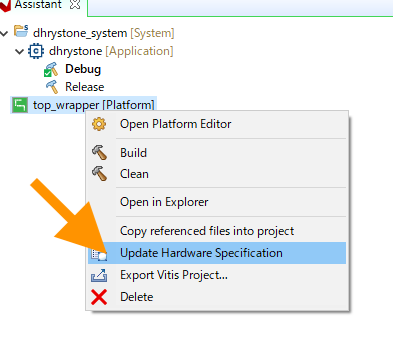

生成されたらVitisで続きを行うためハードウェアファイルをエクスポートします.

メニューバーからFile->Export->Export Hardware …から

OutputでInclude bitstreamを選択し最後まで進めます.

VitisでLチカ

Vitisを起動しVivadoのプロジェクトフォルダ内にワークスペースを指定します.

Create Application Projectからxsaファイルは先程エクスポートしたものを指定し

名前はtest,テンプレートはHello Worldを指定しておきます.

helloworld.cを以下に書き換えます.

#include <stdio.h>

#include "platform.h"

#include "xil_printf.h"

#include "xparameters.h"

#include "xgpio.h"

XGpio gpio_led;

int main()

{

int status;

init_platform();

status = XGpio_Initialize(&gpio_led, XPAR_GPIO_0_DEVICE_ID);

if(status != XST_SUCCESS){

xil_printf("XPAR_GPIO_0_DEVICE_ID initialization failed.\n");

return XST_FAILURE;

}

XGpio_SetDataDirection(&gpio_led, 1, 0x0);

print("Hello World\n\r");

print("Successfully ran Hello World application");

int i = 0, t;

while(1)

{

i = (i + 1)%8;

XGpio_DiscreteWrite(&gpio_led, 1, i);

//Wait

for(t=0;t<5000000;t++){}

}

cleanup_platform();

return 0;

}

プロジェクトをビルドします.

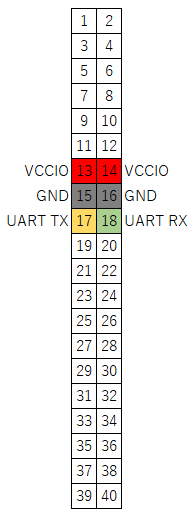

シリアル通信モジュールをFPGAと接続します.

ピンアサインは以下のとおりです.

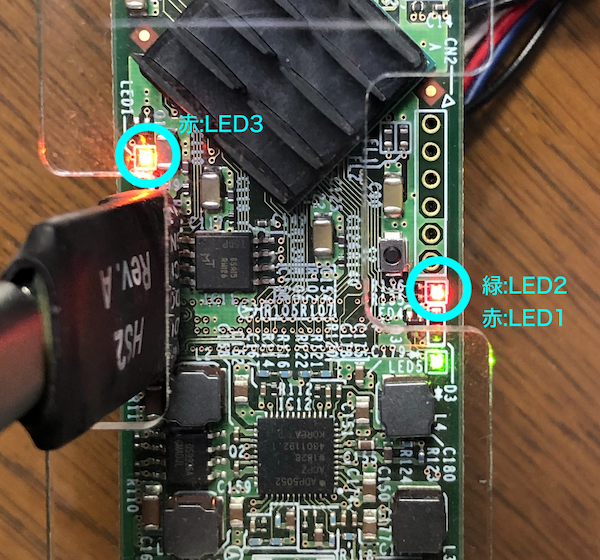

実際に実行してみましょう

上部のメニューからDebug Configurationを開きSingle Application Debugを

ダブルクリックしデバッグ用の設定を作成します.

デバッグを開始してResumeボタンを押せばシリアル通信で文字列が出力され

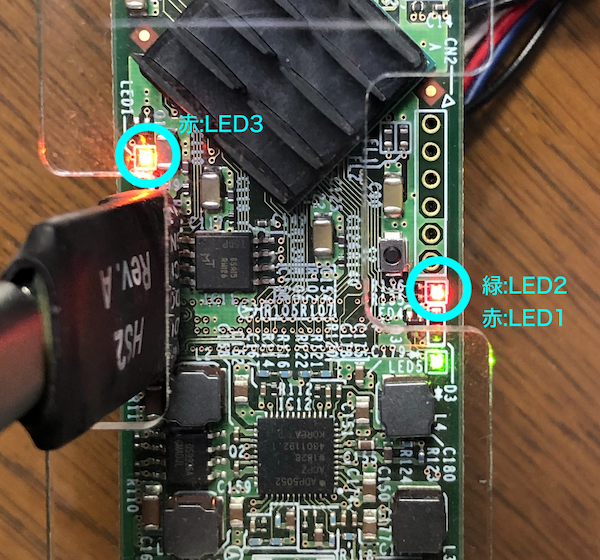

LEDがチカチカします.

無事に動作確認ができました!

まとめ

ボードファイルを使うことで比較的簡単にブロックダイアグラムで

組むことができるようになりました.

主なピンアサインをxdcファイルで指定する必要がなく明瞭になるのと

間違いが抑えられることから便利な仕組みです.

このボードファイルを作ることは結構面倒なのでそこがネックですが…

コメント

[…] 前回作成したボードファイルを使用します. […]