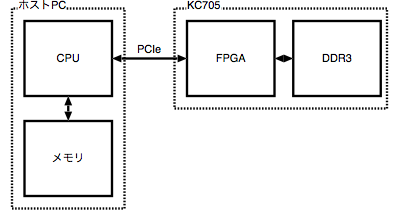

「EDKでPCIe+DDR3のアクセラレータフレームワークを作る(2)」で用意したEmbedded Processorの各インスタンスのパラメタを設定し,適切に接続,AXI上のアドレスをふって完成させます.細かな設定のすべてを書くと,書くのも読むのも大変なので,具体的な値は,「EDKでPCIe+DDR3のアクセラレータフレームワークを作る(1)」のサンプルプロジェクトを参照してもらえれば,と思います. この作業が終わったら,最後に「EDKでPCIe+DDR3のアクセラレータフレームワークを作る(4)」で紹介するトップモジュールを用意して完成です.

各インスタンスのパラメタの設定

コアに設定するパラメタの多くは,Core GeneratorでIPコアのインスタンスを生成するときに設定するものと同様です.AXIがらみのパラメタの多くは,デフォルト値のままで今回はOKです.各インスタンスのパラメタを設定するためには,Bus Interfaceペインに表示されている項目名をダブルクリックして設定ダイアログを開きます.

PCIeの設定

今回の主要な設定項目は,下記の通りです.もしGen2に対応させたければ,5.0GT/s PCIe…にチェックすればいいと思われます.AXI BARは,ここでとりあえず2つ使うように設定しておいてアドレスは後で設定します.

| Common Parameter Settings | |

| Select the Lane Width for the PCIe | 4 |

| Enable for Legacy Interrupt Pin Usage | ON |

| PCIe Block Settings | |

| Used to specify the 7-Series silicon version for accurate GT settings | 3.0 |

| AXI BAR | |

| Number of AXI Address Apertures (AXI BARs) | 2 |

| PCIe BAR0 Mapped from AXI BAR0 | 0x00000000 |

| PCIe BAR1 Mapped from AXI BAR1 | 0x40000000 |

| PCIE BAR | |

| Number of Accessible PCIe Apertures | 2 |

| Slect to configure PCIe BAR Aperture Width to 6-bit. | ON |

| Size of PCIe BAR 0 space (Power of 2) | 17 |

| Size of PCIe BAR 1 space (Power of 2) | 28 |

| AXI BAR 0 Mapped from PCIe BAR0 | 0x00000000 |

| AXI BAR 1 Mapped from PCIe BAR1 | 0x40000000 |

ここで,一番重要なのが,Used to specify the 7-Series silicon version for accurate GT settingsです.ハードIPに対するパラメタ設定に関わるのか,この値を間違うと,まったくPCから認識されず悲しい思いをすることになります.ちなみに,”3.0″という値はGESのチップに対応した値で,もし,IES(Initial Sillicon)なチップの場合は1.0を選択しなければいけません.

DDR3の設定

基本的に設定すべき箇所はありません

GPIOの設定(1)

GPIOは3ステートで使用できますが,このGPIOは主に出力ポート,すなわちメモリライトで書き込まれた値をFPGA内のロジックに出力するポートとして使うことにします.

| Channel 1 | |

| Channel 1 3-state Default Value | 0x00000000 |

GPIOの設定(2)

こっちのGPIOは,デフォルトとして入力ポート,すなわちロジックが設定した値をメモリリードで読み出すために使うことにします.上とは逆に,次のように設定します.

| Channel 1 | |

| Channel 1 3-state Default Value | 0xFFFFFFFF |

axi4lite_0_to_axi4_0_connectorの設定

アドレスレンジとして2種類持てるように設定してありますが,それは不要なので,一つにします.

| Addresses | |

| Slave AXI Number of ADDR Ranges | 1 |

Master-Slave間の接続網を構築する

AXIの世界では,データの読み書きをするモジュールがマスタ,データを読み書きされるモジュールがスレーブになります.例えば,メモリコントローラはそれ自体が他のインスタンスに読み書きするわけではないのでスレーブ,PCIeのように,他のインスタンスに読み書きしたり,他のインスタンスから読み書きされたりするようなコアは,マスタとスレーブの両方を持っています.

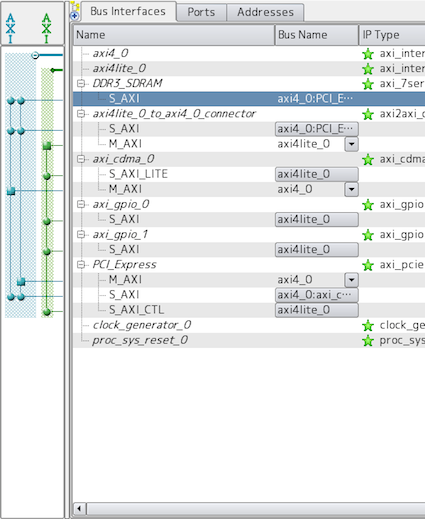

XPSでは,それらマスタ,スレーブのインスタンス同士の接続を組み合わせた接続網を作ることができます.といっても,そう難しい作業ではなくて,Bus Intefacesペインの横にあるペインで接続したい端点同士をクリックして所望の網構成を作成することができます.

下の画像が,今回構築した網構成です.四角がマスタ,丸がスレーブに相当します.

今回BSBで作ったプロジェクトでは,メインのデータをやりとりする網と,制御関係のデータをやりとり網の2段構成になっていたので,そのまま踏襲することにしていますが,基本的には,すべてのマスタがすべてのスレーブにアクセスできるように,接続しています.

少しややこしいのですが,たとえば,PCIeのインスタンス(PCI_Express)のマスタ(M_AXI)は,DDR3_SDRAM,axi4lite_0_to_axi4_0_connector,自分自身であるPCI_Expressの3つのスレーブと接点を設けています.ここで,axi4lite_0_to_axi4_0_connectorのスレーブへの読み書きは,axi4lite_0_to_axi4_0_connectorのマスタにつながったスレーブへの読み書きとしてブリッジされます.従って,結果として,PCI_ExpressのM_AXIは,axi_cdma_0,axi_gpio_0,axi_gpio_1,PCI_ExpressのS_AXI{,_LITE,_CTL)への読み書きができる,ということになります.

AXIアドレス空間の設定をする

Embedded Processorの設定も,もう一息です.ここでは,各インスタンスをAXIのアドレス空間上にマッピングします.ここでは,次のように設定しましょう.

| Instance | Base Name | Base Address | High Address | Size |

| axi4lite_0_to_axi4_0_connector | C_BASEADDR | 0x00000000 | 0x0001FFFF | 128K |

| PCI_Express | C_BASEADDR | 0x00000000 | 0x00000FFF | 4K |

| axi_cdma_0 | C_BASEADDR | 0x00001000 | 0x00001FFF | 4K |

| axi_gpio_0 | C_BASEADDR | 0x00002000 | 0x00002FFF | 4K |

| axi_gpio_1 | C_BASEADDR | 0x00003000 | 0x00003FFF | 4K |

| PCI_Express | C_AXIBAR_0 | 0x10000000 | 0x10001FFF | 8K |

| PCI_Express | C_AXIBAR_1 | 0x20000000 | 0x2FFFFFFF | 256M |

| DDR3_SDRAM | C_S_AXI_BASEADDR | 0x40000000 | 0x7FFFFFFF | 1G |

アドレスは,Addressesタブで俯瞰的に設定できます.ただ,いまいち使いづらいのですが,あらかじめサイズを指定しておかないと,アライメントの関係で開始アドレスを思ったように指定できないので注意しなければいけません.

設定の要点としては,

- axi4lite_0_to_axi4_0_connectorのアドレス空間内に,ぶら下げているインスタンスのスレーブのアドレス空間を設定していること

- AXI BAR 0 Mapped from PCIe BAR0に設定した0x00000000をaxi4lite_0_to_axi4_0_connectorに設定することで,ホストPCでPCIeのBAR0へのアクセスを各インスタンスの制御系のメモリアクセスにマッピングしている

- AXI BAR 1 Mapped from PCIe BAR1に設定した0x40000000をDDR3_SDRAMのC_S_AXI_BASEADDDRに設定することで,ホストPCからPCIeのBAR1へのアクセスをダイレクトにDDR3にマッピングしている

の3点でしょうか.

ポートの接続を完成させる

最後に,Portsタブを開いて,すべてのインスタンスの未割当のポートを処理してしまいましょう.基本的な方針は,次の二つです.

- 各インスタンスのクロックはユーザクロックとする100MHzを作っているclock_generator_0::CLKOUT3にする

- クロック以外のIOは後でトップモジュールで結線するために,External PortsとしてEmbedded Processorの外に引き出す

もちろん,ユーザクロックは所望のクロックにすることができます.

また,この時点でクロック入力ポートにクロック制約を指定できるようです.私の場合,PCIeのリファレンスクロック入力であるPCI_Express_REFCLK_pinの周波数が未入力状態だったので,100000000 (100MHz)を入力しておきました.

コメント