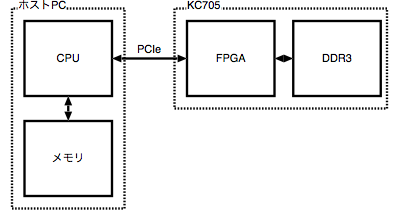

「EDKでPCIe+DDR3のアクセラレータフレームワークを作る(3)」までで,フレームワークのコアとなるEmbededd Processorの構成が完成しました.最後に,Embedded Processor内で完結しない制御信号や外部とのインターフェースを整えるトップモジュールをHDLとUCFファイルを用意します.

今回のシステムは,ほぼEmbedded Processorで構成したままなので

- PCIeのクロックを生成

- リセットやPLLのロック信号を適切に接続する

- PCIeコアの割り込み制御のハンドリング

くらいが,トップモジュールに記述しなければならない事項です.

トップモジュールのひな形をつくる

Embedded Processorのインスタンスを生成するラッパーHDLモジュールはツールにつくってもらうことができます.作り方は,Core GeneratorでHDLのInstanceテンプレートを作る手順と似ていて,

- ISEのHierarchyペインでEmbedded Processor(今回はaxi_cdma_system_i)を選択

- ProcessesペインのGenerate Top HDL Sourceをダブルクリックする

で完了です.

PCIeのクロックを接続

PCIeのリファレンスクロック入力は差動信号です.XPS内で差動→単信号に変換することもできるようですが,よくわからなかったので,トップモジュールでケアします.といっても,普通にGTE2のインスタンスを作るだけですね.

U_GTE2 : IBUFDS_GTE2 port map(

O => pcie_ref_clk,

ODIV2 => open,

I => PCIE_REFCLK_P,

IB => PCIE_REFCLK_N,

CEB => '0'

);

もちろん,pcie_ref_clkはsignal宣言しないといけません.

リセット入力信号の生成

今回,PLLとしては,全体のクロックマネージャとPCIe内部のものの2系統があります.そこで,

proc_sys_reset_0_Dcm_locked_pin <= clock_generator_0_LOCKED_pin and PCI_Express_mmcm_lock_pin;

とかして,クロックマネージャとPCIeのPLLロック信号をリセット回路にフィードバックします.

PCIeコアの割り込みのハンドリング

PCIeの割り込みテストをするために,GPIOを使ってFPGAからホストPCへのPCIe割り込みを制御ができるようにしてみます.GPIOに’1′ を書くと,割り込みが発生するというわけです.

process (user_clk)

begin if user_clk'event and user_clk = '1' then

if user_reset = '1' then

PCI_Express_INTX_MSI_Request_pin <= '0';

axi_gpio_1_GPIO_IO_I_pin <= X"ABADCAFE";

else

PCI_Express_INTX_MSI_Request_pin <= axi_gpio_0_GPIO_IO_O_pin(0);

if axi_gpio_0_GPIO_IO_O_pin(0) = '1' then

axi_gpio_1_GPIO_IO_I_pin <= X"DEADBEAF";

else

axi_gpio_1_GPIO_IO_I_pin <= X"ABADCAFE";

end if;

end if;

end if;

end process;

ホストPCには,割り込みが起きたら,「GPIO1の値を読んで割り込み要因であることを確認し,割り込み制御ピンを下げる」という処理をするドライバを用意すればいいですね.

最後に

今回は,とりあえずフレームワークを作るまでの手順を紹介しました.しかし,実際には自分のロジックを組み込まなければいけません.

自作コンポーネントを組み込む場合には,まじめにAXIコアとして作成して,IPカタログにimportして組み合わせるというのが王道です.ただ,テスト段階では,Utilityの下にある,AXI External Master Connector/AXI External Slave ConnectorというモジュールでEmbedded Processorの外にAXIメモリ空間の信号を引き出して,独自モジュールと接続するという方法をとることもできます.

Let’s enjoy with AXI♪

コメント