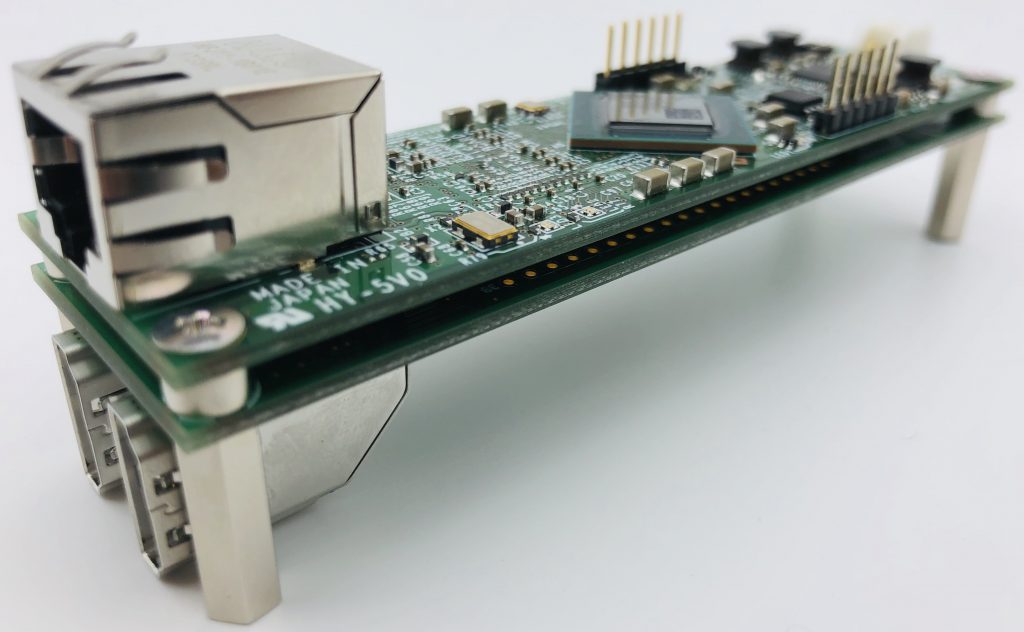

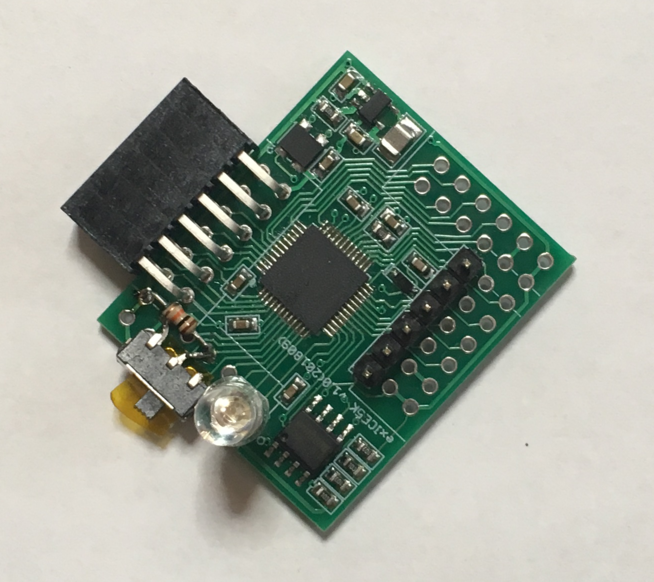

e-trees.Japanでは, exStick の後継として exStickGE を開発,発売しました.exStickでは100MbEだったネットワークインターフェースが,GbEへとパワーアップ.もちろん,e7UDP/IP IPコアが付属しますので,簡単にネットワーク接続可能なハードウェアの開発ができます.

また,256MBのDDRメモリを搭載していますので,ちょっとしたソフトコアの実装にも利用できます.オンボードの汎用I/OはPMOD1系統とちょっと寂しいですが,高密度コネクタを介してFPGAのI/Oにアクセスできます.

同時発売の画像I/Oボードを使えば,2系統のHDMIと2系統のMIPI-CSIを利用できます.

…という前置きはさておき,まずはテストプログラムによるネットワークアクセスの様子を紹介します.

テストロジック

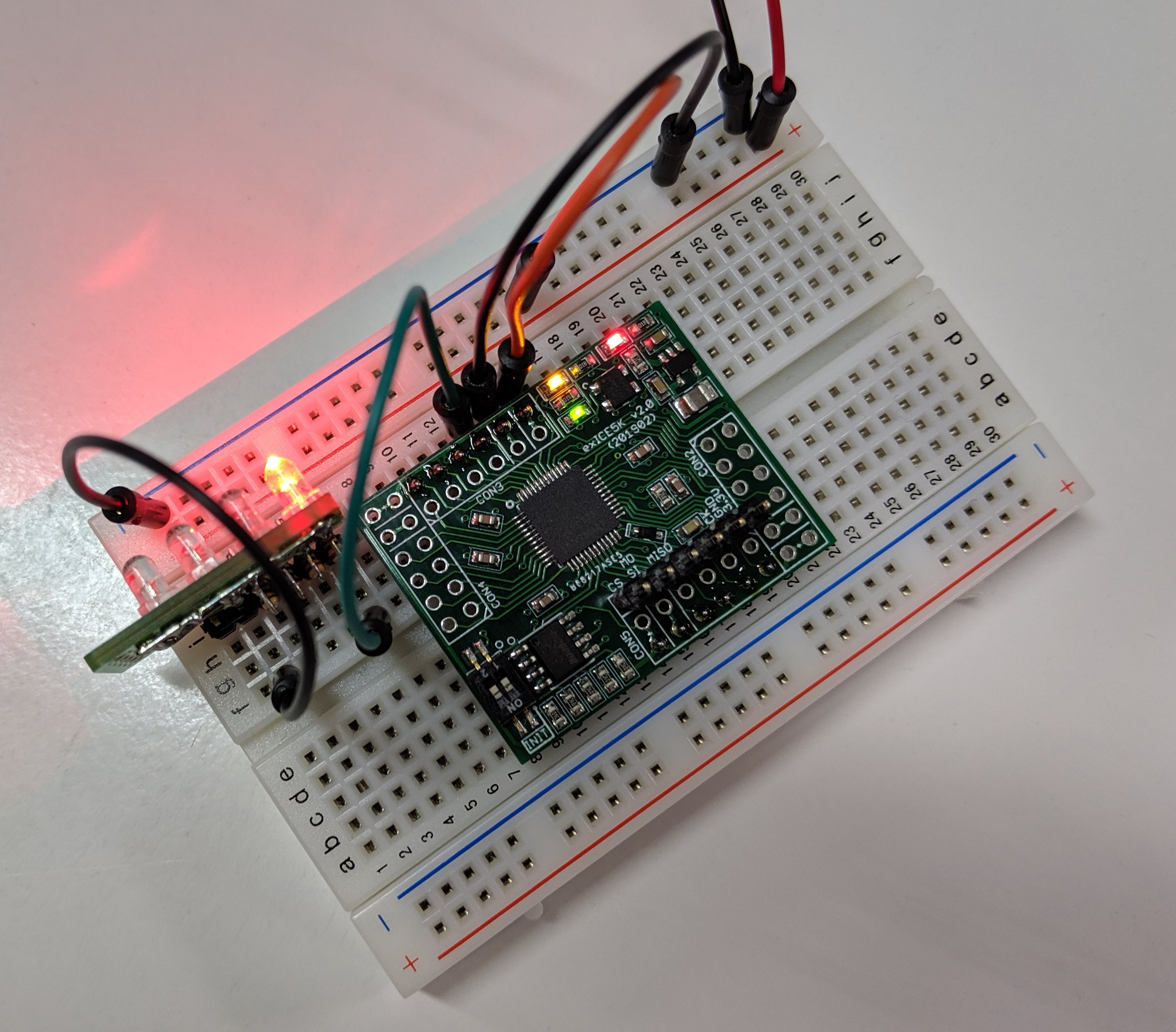

テストロジックは,DDRメモリの初期化とUDP/IPコアの動作確認ができる,というものです.

プロジェクト一式 – exStickGE_udpip_loopback (GitHub)

cloneして,Vivadoで合成すればOKです(手元では,Vivado 2019.1で確認しました).ただし,合成には,e-trees.Japanの提供するe7UDP/IP IPコアを edif ディレクトリ に配置する必要があります.

% git clone https://github.com/e-trees/exstickge_samples.git % cd exstickge_samples/exStickGE_udpip_loopback % vivado -mode batch -source create_project.tcl

これで,top.bit が,exstickge_loopback/exstickge_loopback.runs/impl_1 の下にできあがります.

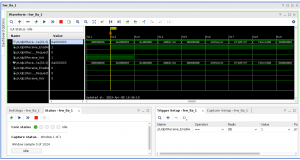

FPGA内でのUDP/IPパケットの様子

ILAをいれて合成すると,Hardaware ManagerでFPGA内のUDP/IPパケットの様子を眺めることができます.10.0.0.3(exStickGEに割り当てたIPアドレス)向けのパケットがFPGA内を流れている様子をキャプチャしたところです.Enable信号がアサートされている間のDataがホスト(10.0.0.1)から送られたパケットデータです.

(クリックすると大きくなります)

ちなみに,これは,次のようなUDP送受信スクリプトを用意して実行してみたものです.

受信側

#!/usr/bin/ruby

require "socket"

socket = UDPSocket.open()

socket.bind("0.0.0.0", 0x4000)

p socket.recv(65535)

socket.close

送信側

#!/usr/bin/ruby

require "socket"

socket = UDPSocket.open()

sockaddr = Socket.pack_sockaddr_in(0x4000, "10.0.0.3")

socket.send("Hello World", 0, sockaddr)

socket.close

次は

DDRメモリの活用,画像入出力の活用事例を紹介します.

コメント