XilinxのVC709に搭載されているFPGA XC7VX690TはGen3 Integrated Block for PCIeを内蔵しています.KC705やVC707搭載のコアと違ってGen3 x8まで対応しています.

PCIe Gen2までのコアと違って,FPGA→PCのデータ転送(rc/rq)とPC→FPGAのデータ転送(cc/cq)の2種類のAXI4ストリームでユーザロジックと接続するようになっているのが大きな特徴でしょうか.

そのせいか,2014年8月時点ではAXI-MMに変換して,DMAコントローラや他のコンポーネントと簡単に接続するためのIPコアがXilinxからは,まだ提供されていません.サードパーティ製のIPコアを使うか自分で実装する必要があります.

というわけで,実装して速度を評価してみました…残念ながら評価につかったホストPCのCPUがCore i3だったためGen2 x8での評価なのですけれど.

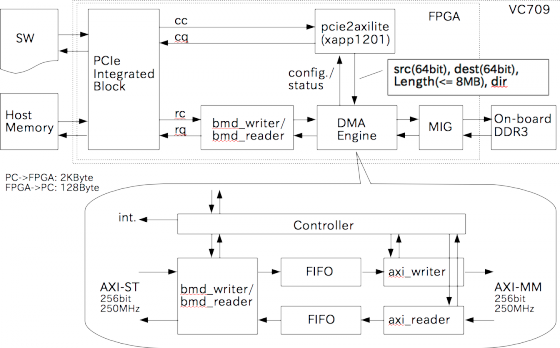

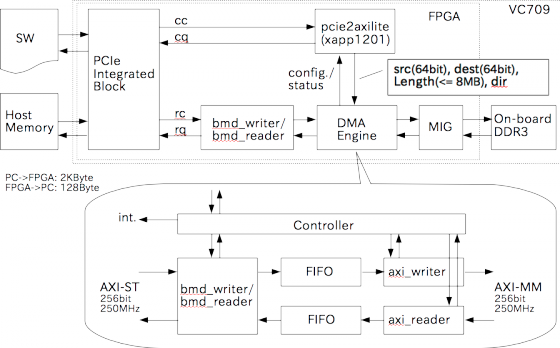

システムアーキテクチャ

評価のために実装したシステムのアーキテクチャは次の図のようなものです.

PC→FPGAの経路はxapp1201を参考にしました.どちらかといえば,こちら側のハンドリングの方が面倒なので,大変ありがたいアプリケーションノートです.

結果

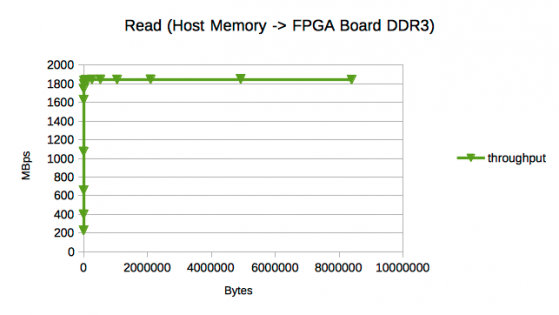

リード

ホストPCのデータをFPGAが読み込みボード上のDDR3に読み出す経路の結果は次の通りです.1.85GBpsくらいが上限のようです.

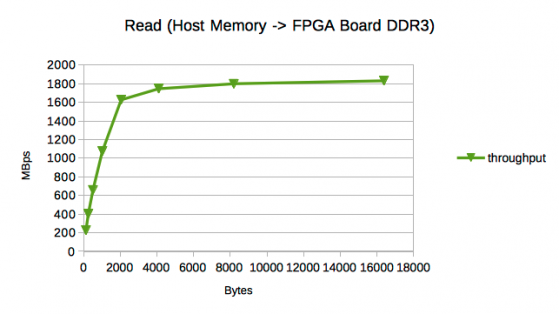

128kBまでを拡大したものは次の通り.

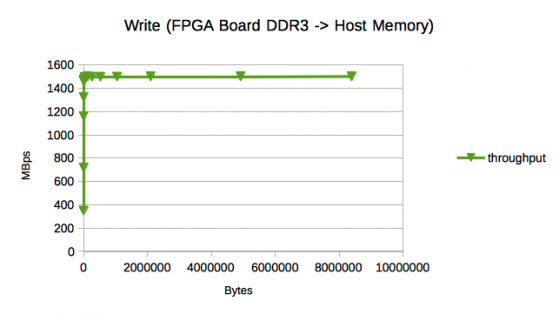

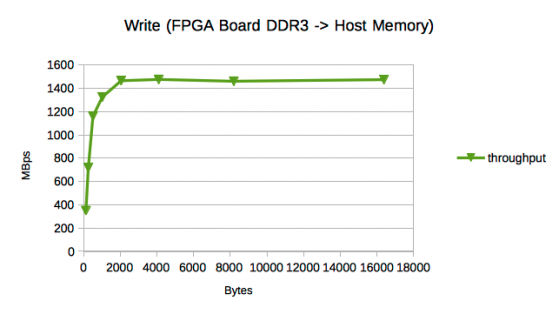

ライト

逆にFPGAがボード上のDDR3上のデータをホストPCのメモリに書き出す経路の結果は次の通りです.こちらは,1.50GBpsくらいが上限.もうちょっとがんばれそうな気もします.

128kBまでを拡大したものは次の通り.

まとめのような

KC705でPCIeの通信性能を測定してみたで紹介した性能に比べて,「ホスト→FPGA」と「FPGA→ホスト」のスループットが,それぞれ2.1倍と1.4倍とい結果が得られました.アーキテクチャが違うのでGen2 x4→Gen2 x8の違いだけとは言えませんが,まあまあ高速になったと言えそうです.

まだだ、まだ終わらんよ

というわけで,FPGA→ホストは性能向上の伸びしろが大きいようなので,もう少しがんばらねば,ですかね.あ,もちろん,近いうちに,Core i5以上のマシンを用意してGen3 x8での性能評価をしてみよう.

宣伝

VC709のようなVirtex-7 FPGA Gen3 Integrated Block for PCIe 3.0用のIPコアをお探しの方は,是非,弊社までご連絡いただければと思います.

コメント