UPLの理解を進めるために、外部のFPGA等の回路からIOピンをパタパタしてUDPの送信/受信を行えるexStick用のコンフィグデータを作りました。これを使えば、AlteraユーザさんでもXilinxの開発環境を使わずにexStickのUDP機能を簡単に試していただけます。

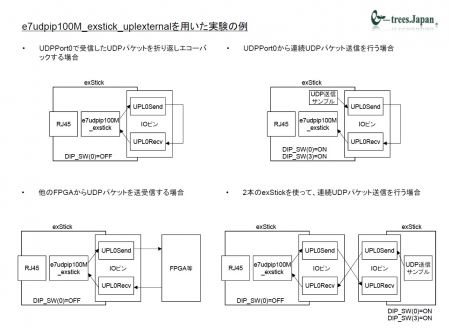

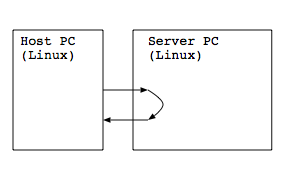

どのようなことができるかといいますと、次の図を見てみてください。

e7udpip100M_exstickコアでは、2つのUDPポート番号での送受信ができますが、そのうちのUDPPort0を外部IOピンに接続しました。

ただしIOピンの本数が少ないので32bitUPLを8bitUPLに変換しています。

クロックはソースシンクロナスですので、UDP受信パケットが出てくるUPL0Sendポートからはクロックが出力されています。またUDP送信パケットを入力するUPL0Recvポートにはクロックを入力してください。

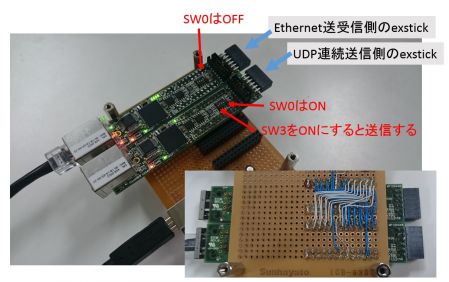

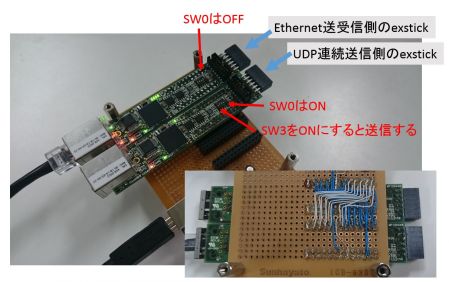

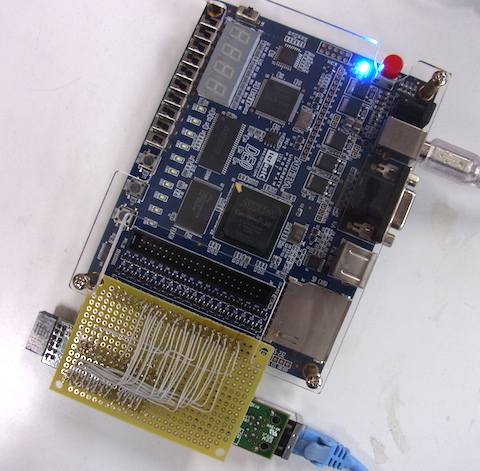

2本のexStickを使って次の写真のように作ってみました。1つのexStickからUDPパケットを送り出して、もうひとつのexStickでイーサネットフレームにくるんでネットワークに送出してくれます。

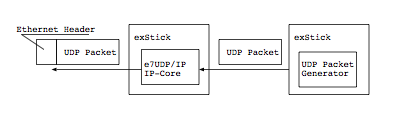

動作イメージは次の図の通りです.

このサンプルはexStickをご購入いただいたお客様には無償で公開しております。exStickに同梱しておりますユーザ名とパスワードでサポートページにアクセスしてダウンロードしてください。

RevB/RevCどちらのexStickでも動作します。

ご質問等ありましたら、お気軽にお問い合わせください。

コメント