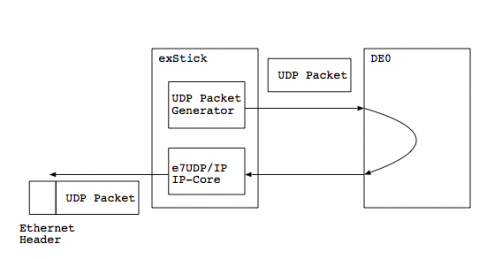

exStickで外部回路からUDPパケットを送受信するの続編として,このサンプルを使ってexStickとDE0(Altera Cyclone III)を接続してみました.といっても,DE0では単にパケットを通過させているだけ,なのですが.

exStickをモジュールとして使う事で,手軽にUDP入出力機能をシステムに組み込むことができますね.

どういうこと?

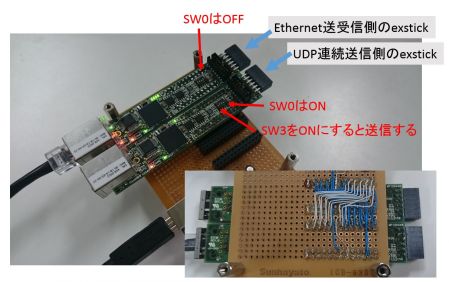

こういうこと,です.

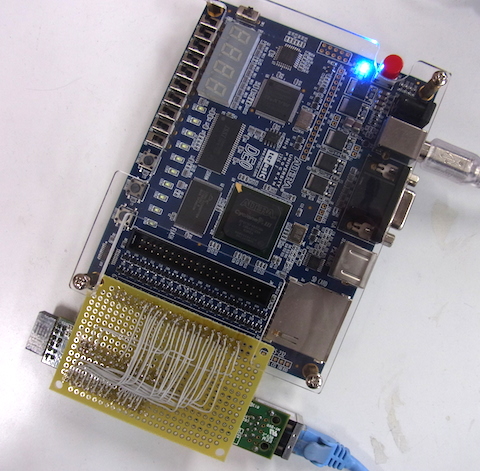

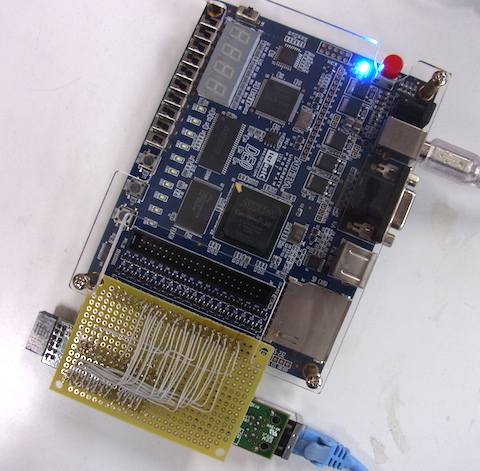

DE0のJ5コネクタとexStickを接続しています.万能基板の裏側についている(イーサコネクタがささっている)モジュールがexStickです.

つなぎ方

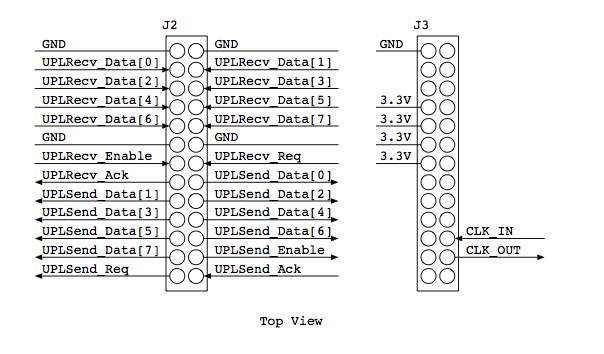

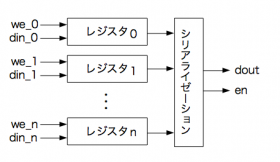

exStickからは,UDPポート0の入出力が次のようにひきだされています.データ8本+制御信号3本+クロックの組が送受信で2組なので,合計22本ですね.

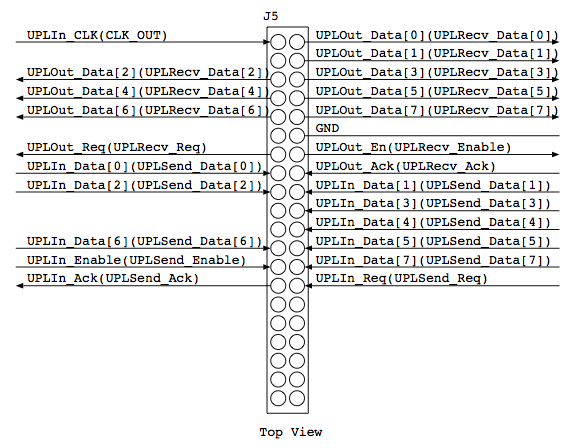

Altera側はJ5を使いました.配線はこんな感じ.Altera側の入力(In)がexStickからの出力(Send),Altera側の出力(Out)がexStickの入力(Recv)に接続されることに注意します.

Altera側のFPGAのコード

入ってきたものを出力するだけ,です.ちなみに,ここでは,ただ折り返しているだけですが,もし内部で処理する場合には,入力されるデータ(UPLIn)のデータ/制御信号はUPLIn_Clkに同期して取り込み,また,出力するデータ(UPLOut)はUPLOut_Clkに同期して送り出します。

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity exstick_rev is

port

(

UPLIn_Clk : in std_logic;

UPLIn_Data : in std_logic_vector(7 downto 0);

UPLIn_Req : in std_logic;

UPLIn_En : in std_logic;

UPLIn_Ack : out std_logic;

UPLOut_Clk : out std_logic;

UPLOut_Data : out std_logic_vector(7 downto 0);

UPLOut_Req : out std_logic;

UPLOut_En : out std_logic;

UPLOut_Ack : in std_logic

);

end exstick_rev;

architecture RTL of exstick_rev is

begin

UPLOut_Clk <= UPLIn_Clk;

UPLOut_Req <= UPLIn_Req;

UPLOut_En <= UPLIn_En;

UPLIn_Ack <= UPLOut_Ack;

UPLOut_Data <= UPLIn_Data;

end RTL;

ピン配置はこんな感じ(qsfに追記します).

set_location_assignment PIN_AB11 -to UPLIn_Clk set_location_assignment PIN_R16 -to UPLOut_Clk set_location_assignment PIN_T15 -to UPLOut_Ack set_location_assignment PIN_AB17 -to UPLOut_Data[7] set_location_assignment PIN_AA17 -to UPLOut_Data[6] set_location_assignment PIN_AA18 -to UPLOut_Data[5] set_location_assignment PIN_AB18 -to UPLOut_Data[4] set_location_assignment PIN_AB19 -to UPLOut_Data[3] set_location_assignment PIN_AA19 -to UPLOut_Data[2] set_location_assignment PIN_AB20 -to UPLOut_Data[1] set_location_assignment PIN_AA20 -to UPLOut_Data[0] set_location_assignment PIN_W17 -to UPLOut_En set_location_assignment PIN_Y17 -to UPLOut_Req set_location_assignment PIN_U12 -to UPLIn_Ack set_location_assignment PIN_R14 -to UPLIn_Data[7] set_location_assignment PIN_AA7 -to UPLIn_Data[6] set_location_assignment PIN_AB7 -to UPLIn_Data[5] set_location_assignment PIN_AA9 -to UPLIn_Data[4] set_location_assignment PIN_AB9 -to UPLIn_Data[3] set_location_assignment PIN_W15 -to UPLIn_Data[2] set_location_assignment PIN_V15 -to UPLIn_Data[1] set_location_assignment PIN_U15 -to UPLIn_Data[0] set_location_assignment PIN_T14 -to UPLIn_En set_location_assignment PIN_T12 -to UPLIn_Req

何ができるの?

たとえば,exStickで外部回路からUDPパケットを送受信するの”UDPPort0から連続UDPパケット通信を行う場合”の場合,exStickで生成されたUDPパケットが,DE0を通過してexStickに戻されてイーサネットポートから出力される様子が確認できます.

これから

DE0は,スイッチやLED,SDカードにVGA出力と豊富なペリフェラルを持っています.せっかくなので,次は,ネットワーク経由(exStick経由)で,それらのペリフェラルにアクセスしてみたいと思っています.

コメント